# Power Electronics: From Semiconductor Basics to Advanced Design and Testing: part 2

Matteo Santoro, Commissione Elettronica e Microelettronica Ordine degli Ingegneri della provincia di Roma

Product Manager Semikron Danfoss.

### **Power Electronics**

4. Power Module Design and Manufacturing

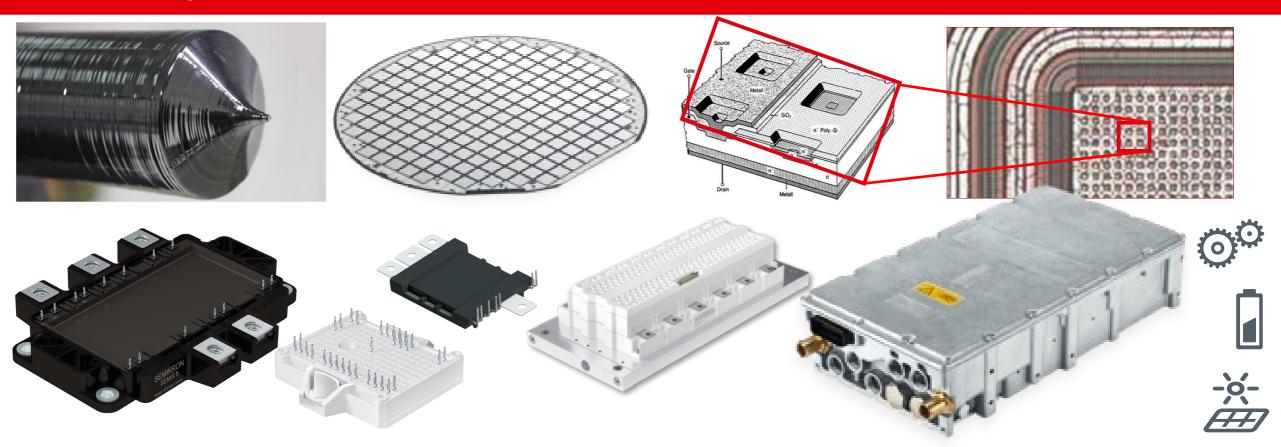

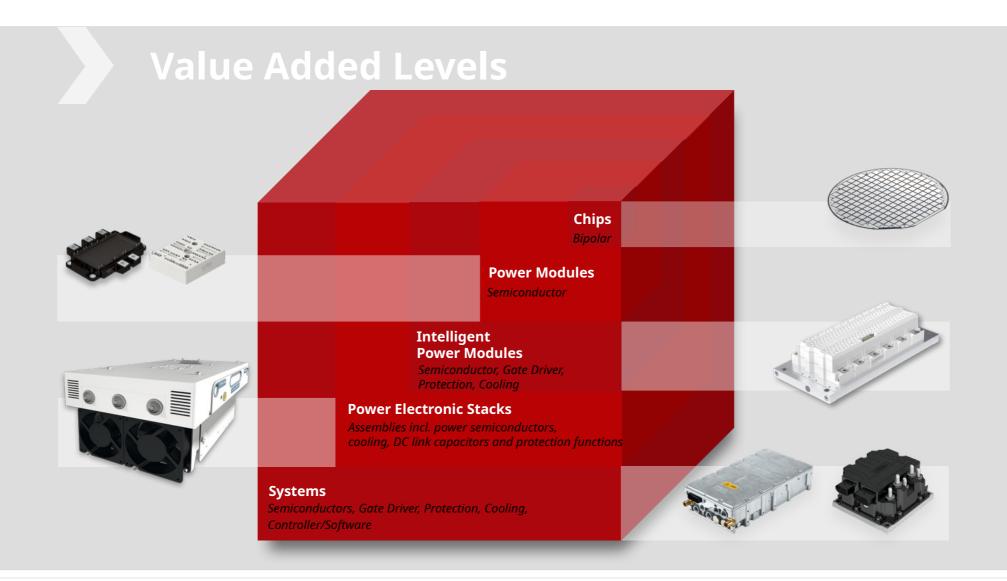

### From Chip to System

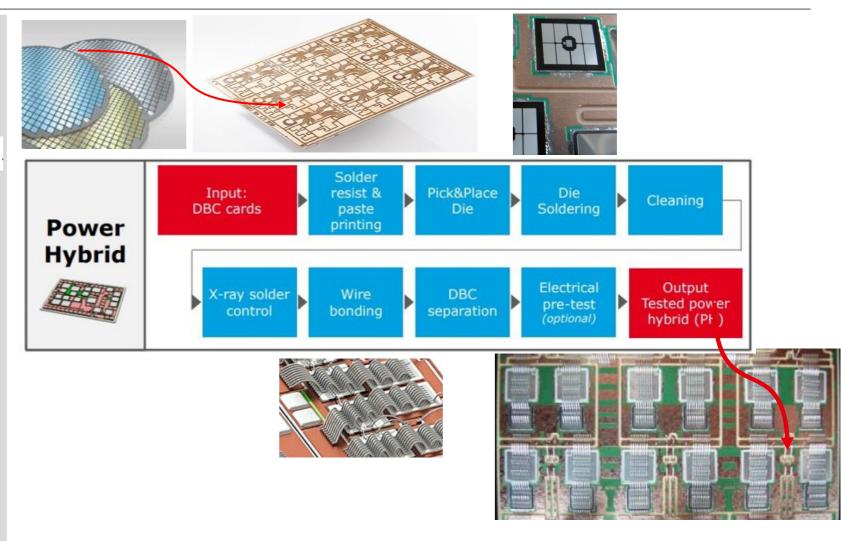

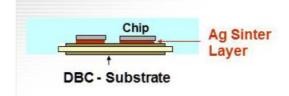

### Manufacturing substrate: «Power Hibrid»

### Thermal capacity for different material's substrate

- $Al_2O_3:24\frac{W}{m\cdot K}$ ,(Allumina)

- AlNda 130 a  $180 \frac{W}{m \cdot K}$  (Alluminio Nitruro).

Thermal expansion coefficient is comparable with silicon

$$Al_2O_3$$

è di  $7.1\frac{ppm}{K}$

$$AlN \ earline{e} \ (4.1 \frac{ppm}{K})$$

silicio (

$$4.0\frac{ppm}{K}$$

)

DCB: Direct Copper Bonded (prelasered or laser-cut in the manufacturing line)

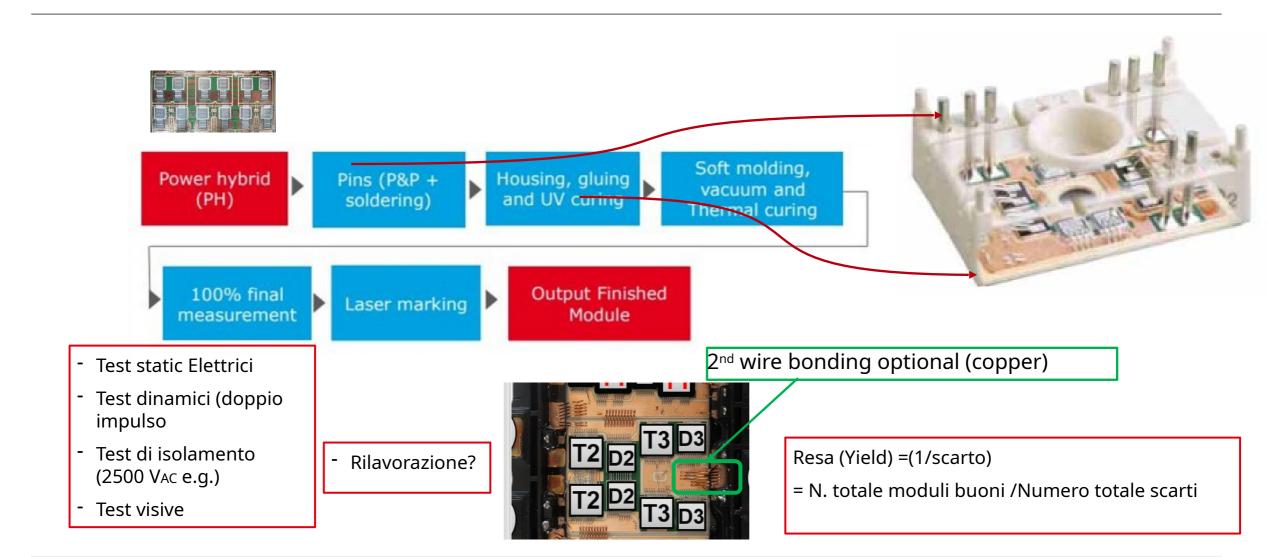

#### Module Manufacturing (dal Power Hibrid) (DA3, DB3...)

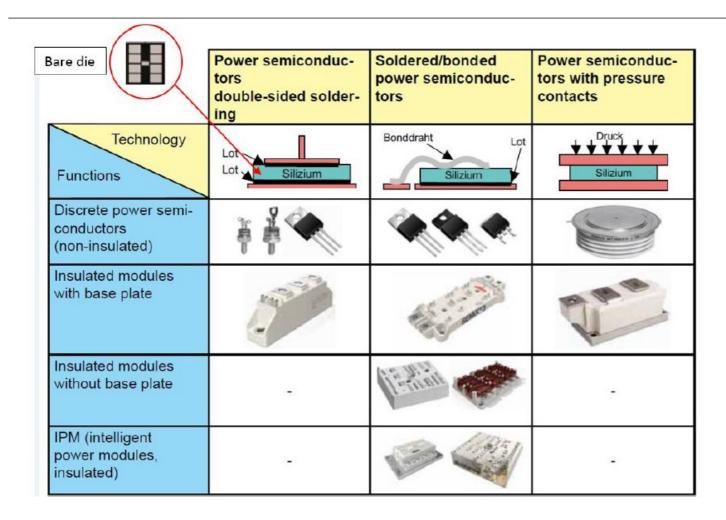

#### **Power Modules Classification**

Figura 1.4: Classificazione dei moduli di potenza in funzione della tecnologia

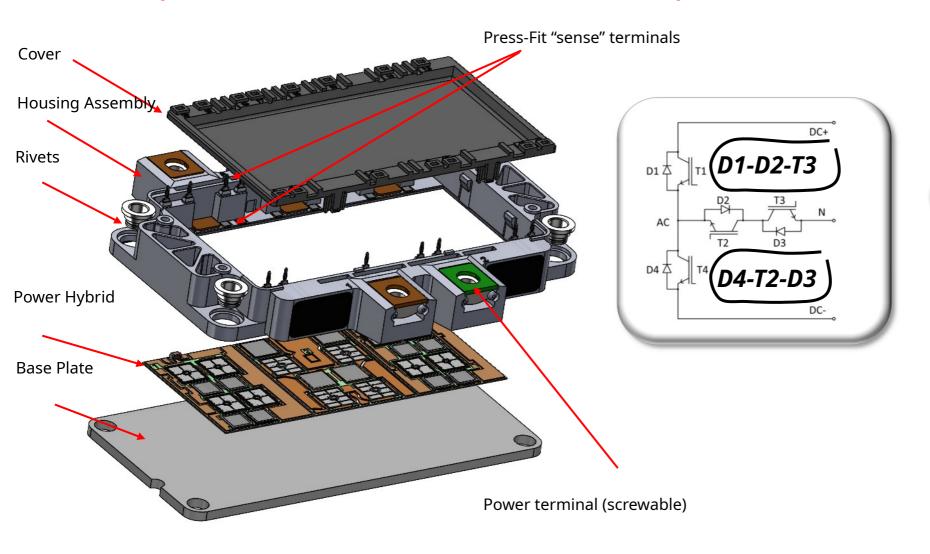

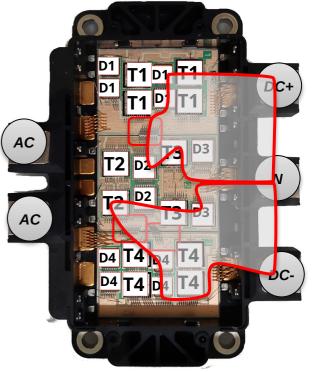

#### Example: Power Module with base-plate

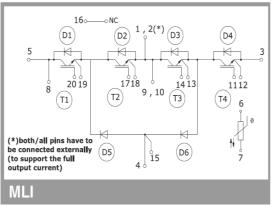

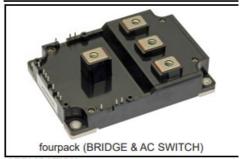

SKD "true" 400A TNPC (SEMiX405TMLI12E4B)

#### ... Driver...

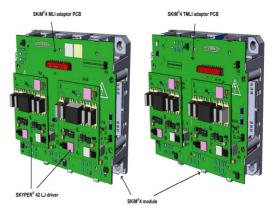

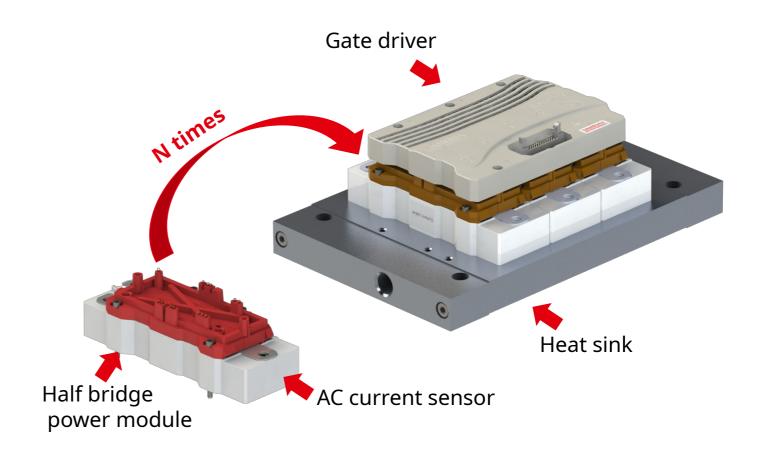

**SKiiM-4&5**

SEMIX-5

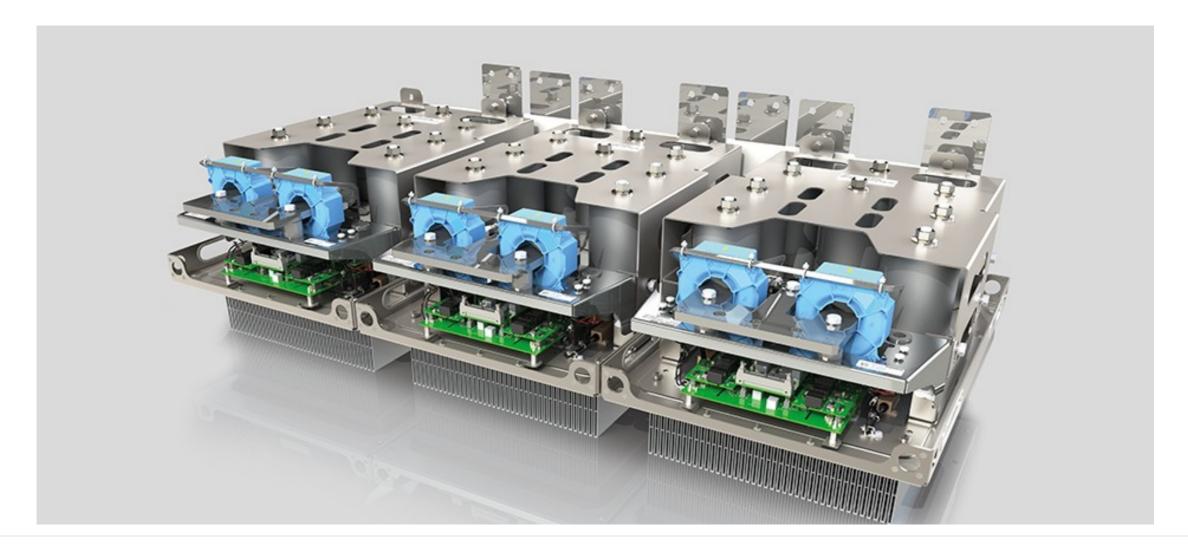

100/125 KW Solar

250 KW Solar

500 KW Solar

#### ...Intelligent Power Module ...

- Intelligent power module with integrated driver, sensors and cooler

- High power halfbridge or sixpack configuration (0.5-2MW)

- Blocking voltage 1200V or 1700V

- Current ratings 500-3600A

- Safety isolated current, temperature and voltage sensors

- Basic protection functions

### ... Stack

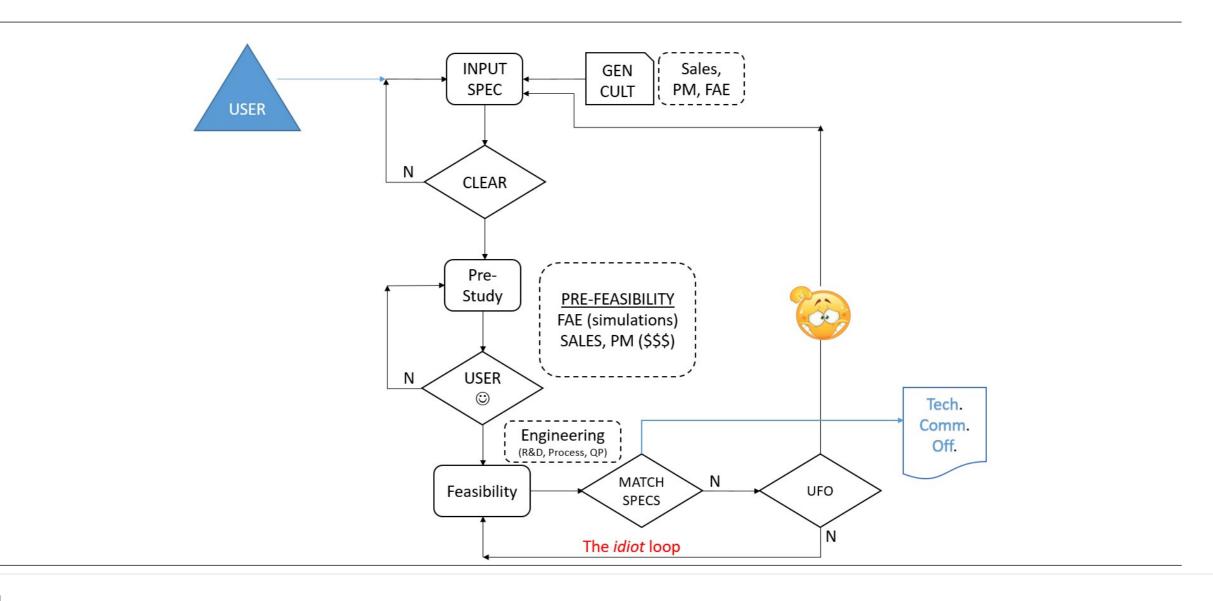

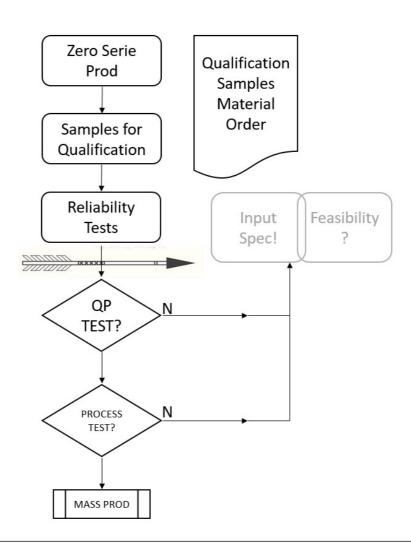

### Design Flow 1/3

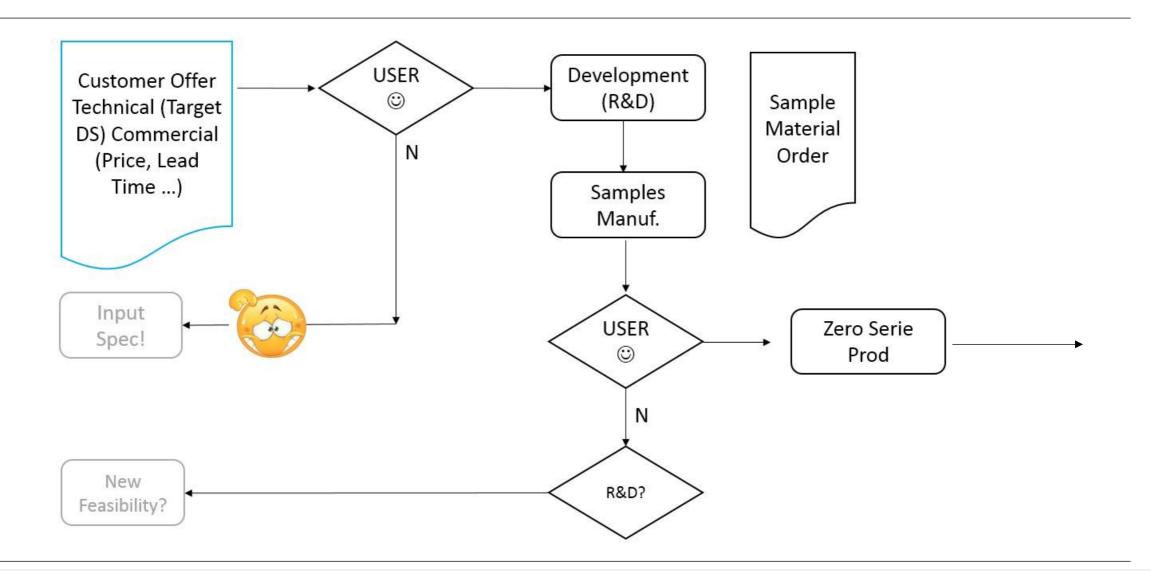

#### Design Flow 2/3

### Design Flow 3/3

### **Power Electronics**

5. Datasheet

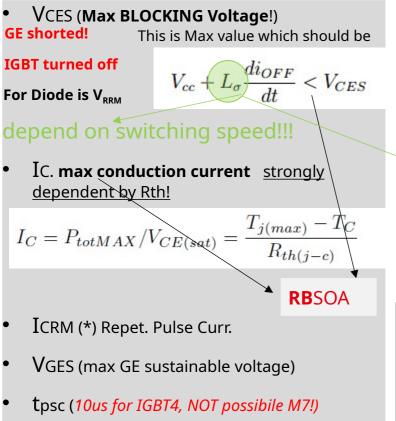

#### Datasheet, Absolute Maximum Ratings

$I_{CRM} = 3 \times I_{Cnom}$

$t_p = 100 \mu s$ ; repetition rate limited by

T<sub>imax</sub>; Duration: <10% of total time

SiC D

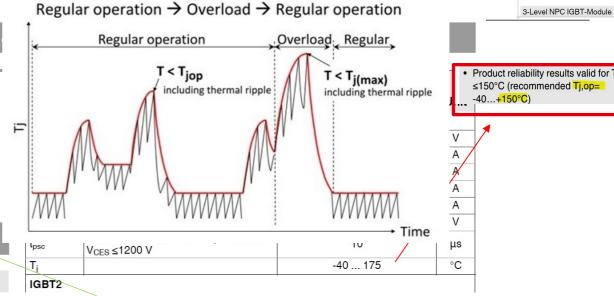

The maximum allowable temperature for the chip during conventional continuous operation is specified in  $T_{i(on)}$ . Please ensure the maximum chip temperature stays at or under  $T_{i(on)}$  during conventional continuous operation. The maximum allowable temperature for a chip during short-term overload or abnormal operation is specified  $inT_{i(max)}$ .

"SHOULD BE" always present but is a MUST for "small chips" like SiC where bond wires are limited in this case IFRM is less then 3 times ICnom!

$I_{FRM}$

ICRM

Tj (Tv,jmax Tj,op)

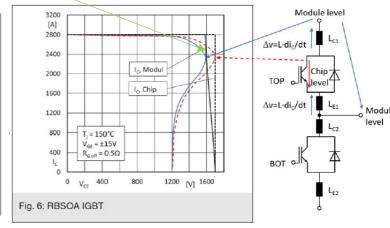

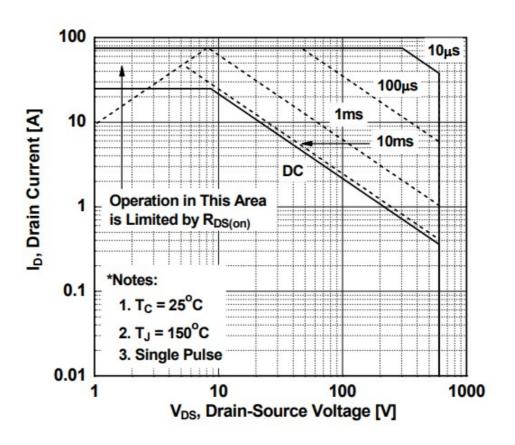

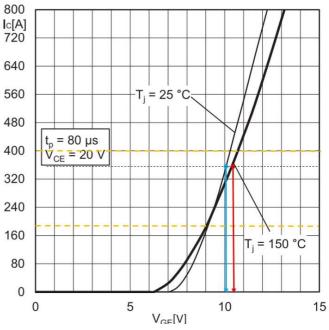

#### SOA (for Linear Amplifier! Not used in Switcing Power Elec.)

- SOA is different is FORWARD current and maximum nominal current

- Not available in modern datasheet

- Depend on the time and limited by Ron

- SOA is mainly used or "linear operation" in CONTINUE operation which is typical of transistor in Active Area (so this is the reason you do not find often in Power Module working in PWM)

Figure 9. Maximum Safe Operating Area

#### FCH25N60N N-Channel MOSFET 600V, 25A, 0.126Ω

#### **Features**

+ R $_{\rm DS(on)}$  = 0.108 $\Omega$  ( Typ.) at V $_{\rm GS}$  = 10V, I $_{\rm D}$  = 12.5A

Rof FCH25N60N N-channel Mosfet

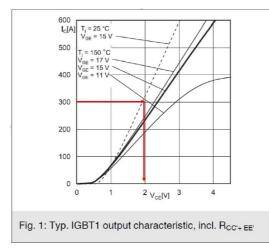

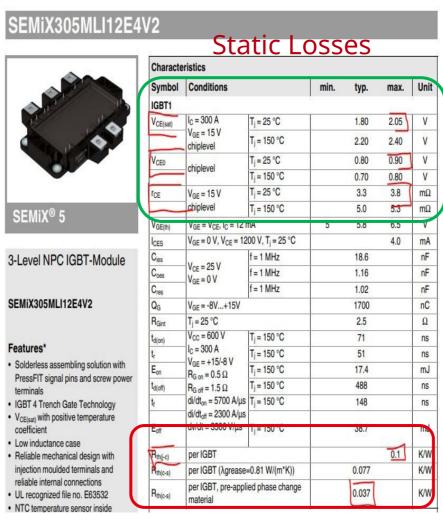

#### Datasheet, STATIC Characteristics

- VCE(sat) (ON

- Chip level Effect of Rcc'-EE'

- VGE(th)

- VCEO, I'CE (values at ON state) VCEtot is provided by the linear model of the ON-State Diode, see after)

$$V_{CE(sat)} = V_{CE0} + r_{CE} \cdot I_{C} egin{array}{ll} \emph{diode} \\ \emph{model} \\ \emph{ON} \end{array}$$

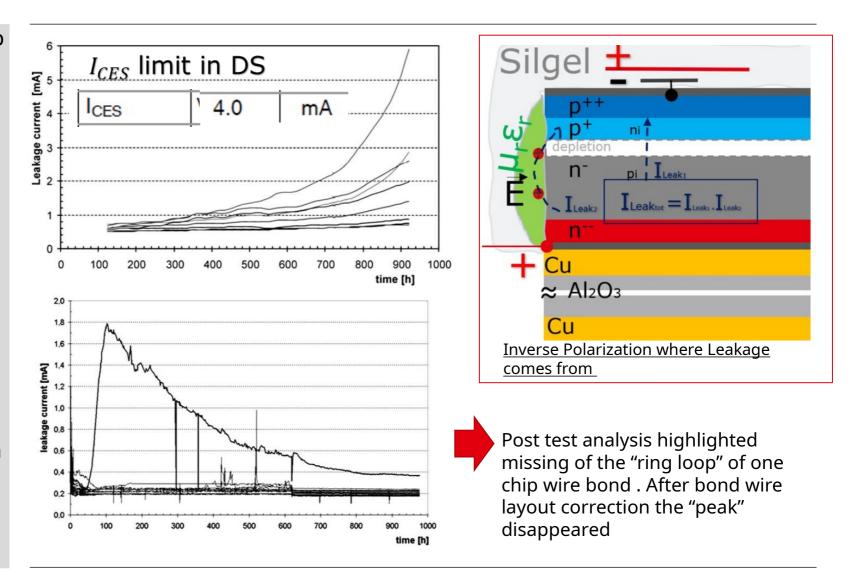

- ICES (max leakage in blocking state, limit for reliability test: It defines ithe value the module should withstand AT THE END of 1000hours HTRB (see reliability); it is PRODUCTION PROCESS dependent!: and COULD BE different with respect ICES value defined at bare dies level! (very often is different)

- Cies, Coes, Cres (directly linked to bare die characteristics)

| Characte             | ristics                             |                         |      |      |      |      |

|----------------------|-------------------------------------|-------------------------|------|------|------|------|

| Symbol               | Conditions                          |                         | min. | typ. | max. | Unit |

| IGBT1                |                                     |                         |      |      |      | •    |

| V <sub>CE(sat)</sub> | I <sub>C</sub> = 300 A              | T <sub>j</sub> = 25 °C  |      | 1.80 | 2.05 | V    |

|                      | V <sub>GE</sub> = 15 V<br>chiplevel | T <sub>j</sub> = 150 °C |      | 2.20 | 2.40 | V    |

| Static Characteristics (tested on wafer), T <sub>vj</sub> =25°C BARE DIE IGC142T8RM |                      |                                                |                |      |      |   |  |

|-------------------------------------------------------------------------------------|----------------------|------------------------------------------------|----------------|------|------|---|--|

| Parameter Symbol Conditions Value Uni                                               |                      |                                                |                |      |      |   |  |

| Parameter                                                                           | Symbol               | Conditions                                     | min. typ. max. |      |      |   |  |

| Collector-emitter breakdown voltage                                                 | V <sub>(BR)CES</sub> | $V_{GE} = 0V, I_{C} = 5.7 \text{mA}$           | 1200           | -    | -    |   |  |

| Collector-emitter saturation voltage                                                | V <sub>CEsat</sub>   | V <sub>GE</sub> =15V, <u>I<sub>C</sub>=45A</u> | 0.97           | 1.15 | 1.32 | V |  |

| Characte             | ristics                                         |                                                            |      |      |      |      |

|----------------------|-------------------------------------------------|------------------------------------------------------------|------|------|------|------|

| Symbol               | Conditions                                      |                                                            | min. | typ. | max. | Unit |

| IGBT1                | •                                               |                                                            | •    |      |      |      |

| V <sub>CE(sat)</sub> | I <sub>C</sub> = 300 A                          | T <sub>j</sub> = 25 °C                                     |      | 1.80 | 2.05 | V    |

|                      | V <sub>GE</sub> = 15 V<br>chiplevel             | T <sub>j</sub> = 150 °C                                    |      | 2.20 | 2.40 | V    |

| V <sub>CE0</sub>     | chiplevel                                       | T <sub>j</sub> = 25 °C                                     |      | 0.80 | 0.90 | V    |

|                      | Chipievei                                       | T <sub>j</sub> = 150 °C                                    |      | 0.70 | 0.80 | V    |

| r <sub>CE</sub>      | V <sub>GE</sub> = 15 V                          | T <sub>j</sub> = 25 °C                                     |      | 3.3  | 3.8  | mΩ   |

|                      | chiplevel                                       | T <sub>j</sub> = 150 °C                                    |      | 5.0  | 5.3  | mΩ   |

| V <sub>GE(th)</sub>  | $V_{GE} = V_{CE}, I_{C} = 12$                   | V <sub>GE</sub> = V <sub>CE</sub> , I <sub>C</sub> = 12 mA |      | 5.8  | 6.5  | V    |

| I <sub>CES</sub>     | V <sub>GE</sub> = 0 V, V <sub>CE</sub> = 12     | 200 V, T <sub>j</sub> = 25 °C                              |      |      | 4.0  | mA   |

| C <sub>ies</sub>     | V 05.V                                          | f = 1 MHz                                                  |      | 18.6 |      | nF   |

| C <sub>oes</sub>     | V <sub>CE</sub> = 25 V<br>V <sub>GE</sub> = 0 V | f = 1 MHz                                                  |      | 1.16 |      | nF   |

| C <sub>res</sub>     | VGE - V                                         | f = 1 MHz                                                  |      | 1.02 |      | nF   |

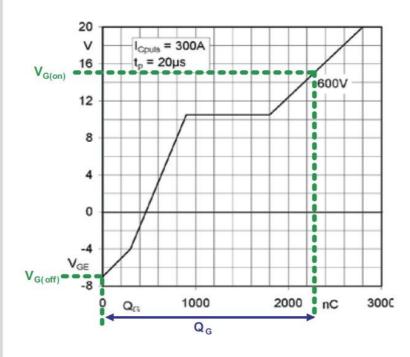

| Q <sub>G</sub>       | V <sub>GE</sub> = -8V+15V                       |                                                            |      | 1700 |      | nC   |

| R <sub>Gint</sub>    | T <sub>i</sub> = 25 °C                          |                                                            |      | 2.5  |      | Ω    |

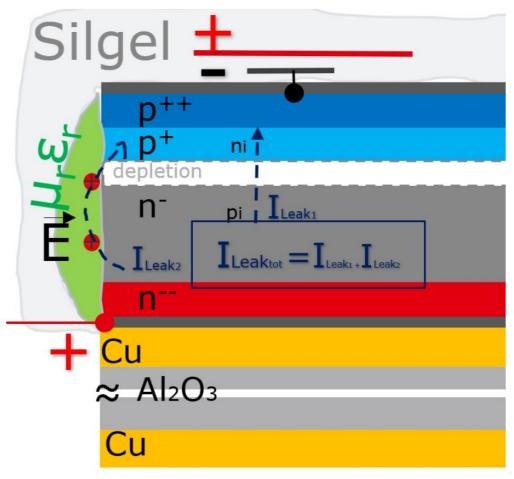

#### Still some consideration on Ices and how is defined in Datasheets

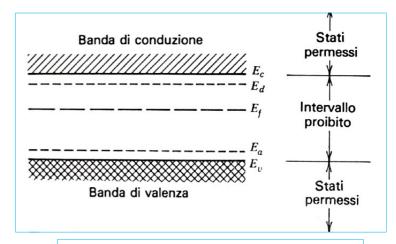

- Even in n-type are presents  $p_i$  (and in p-types  $n_i$ ) which are intrinsic in semiconductors

- This cause  $I_{Leak1}$  in inverse polarization which is "small" compared to forward current (which is very small as  $n_i << p$  and  $p_i << n$ ): some  $\mu A$  in IGBT4 for instance.

- I<sub>leak</sub>=Func(technology, geometry, if several chips in antiparallel, process soldering, reliability tests...)

- Process assembly → introduction of dielectric impurity on the p-n "naked" vertical junction → surface ione impurity further I<sub>Leak2</sub> contributor → I<sub>LeakTot=</sub> I<sub>Leak1</sub>+I<sub>Leak1</sub>> I<sub>Leak1</sub>

- No clean improve. Synther ok (but Ag+!)

- Reliability  $\rightarrow$  1000H HV3TRB further impurity (H2O iones, dendrides, electromigration)  $\rightarrow$   $I_{Leak3}$

$I_{\text{CES}}$  defined in IGBT **MODULE** datasheet usually is higher than ICES in bare die datasheet. And is also linked to TEST SPECIFICATION

Warning: Test specification define also the production scrap rate!

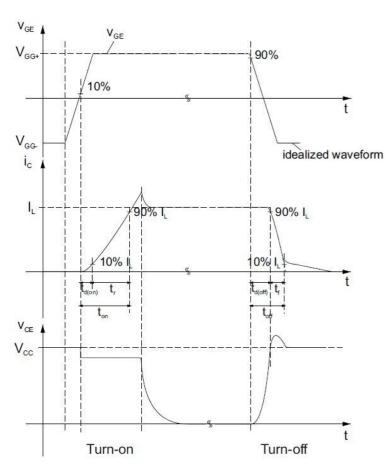

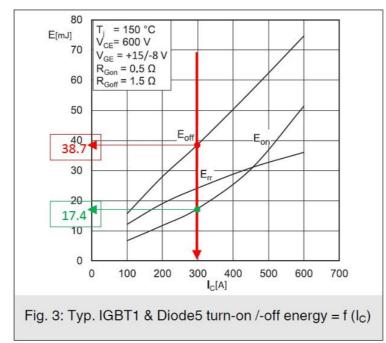

#### Datasheet, Characteristics (switching: Eon, Eoff, rise time, fall time)

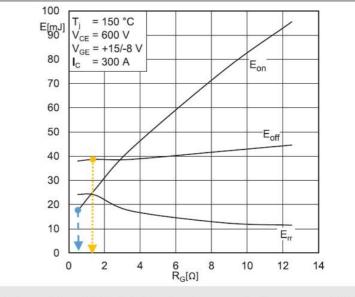

Fig. 4: Typ. IGBT1 & Diode5 turn-on /-off energy = f(R<sub>G</sub>)

Eon

17.4 mJ 488 T<sub>i</sub> = 150 °C 148 38.7 T<sub>i</sub> = 150 °C mJ

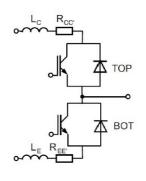

#### Datasheet, Characteristics: commutation speed

SEMIX® 5

$C_{ge}$  in and out with CE shorted

slower

C<sub>ae</sub> with CE direct

| di/dtoff | chip transcond. |

|----------|-----------------|

| dicarr   | $V_{CI}$        |

$$\frac{dt_{Coff}}{dt} = g_{fs} \frac{r_{GE}}{C_{IES} \cdot R_{GOFF}}$$

Overvoltage during switch off

$$dV = L \cdot \frac{di_{OFF}}{dt}$$

Note:

$L = F[Area\_Module + Area\_driver]$

di/dtoff = F[g,C,Rgoff]

di/dtoff QP dynamic bench >> di/dtoff production DPT (x4!)

L(dyn-bench QP) << L(prod DPT)

→ compensation!

| Symbol              | Conditions                                                     |                         | min. | typ. | max. | Unit |

|---------------------|----------------------------------------------------------------|-------------------------|------|------|------|------|

| IGBT1               |                                                                |                         |      |      |      |      |

| C <sub>ies</sub>    |                                                                | f = 1 MHz               |      | 18.6 |      | nF   |

| Coes                | $V_{CE} = 25 \text{ V}$<br>$V_{GE} = 0 \text{ V}$              | f = 1 MHz               |      | 1.16 |      | nF   |

| C <sub>res</sub>    | VGE - O V                                                      | f = 1 MHz               |      | 1.02 |      | nF   |

| $Q_{G}$             | V <sub>GE</sub> = -8V+15V                                      |                         |      | 1700 |      | nC   |

| R <sub>Gint</sub>   | T <sub>j</sub> = 25 °C                                         |                         |      | 2.5  |      | Ω    |

| t <sub>d(on)</sub>  | V <sub>CC</sub> = 600 V                                        | T <sub>j</sub> = 150 °C |      | 71   |      | ns   |

| t <sub>r</sub>      | $I_C = 300 \text{ A}$                                          | T <sub>j</sub> = 150 °C |      | 51   |      | ns   |

| E <sub>on</sub>     | $V_{GF} = +15/-8 \text{ V}$<br>$R_{G \text{ on}} = 0.5 \Omega$ | T <sub>j</sub> = 150 °C |      | 17.4 |      | mJ   |

| t <sub>d(off)</sub> | $R_{G \text{ off}} = 1.5 \Omega$                               | T <sub>i</sub> = 150 °C |      | 488  |      | ns   |

| t <sub>f</sub>      | $di/dt_{on} = 5700 \text{ A/}\mu\text{s}$                      | 1                       |      | 148  |      | ns   |

| E <sub>off</sub>    | di/dt <sub>off</sub> = 2300 A/μs<br>dv/dt = 3500 V/μs          | j = 150 °C              |      | 38.7 |      | mJ   |

from QLAB dyn-Bench which is set for max switching speed and min Rq

Important parameters to design gate driver!

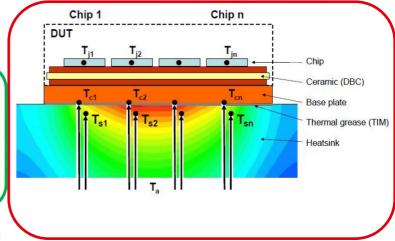

#### Datasheet, Characteristics (Gate Charge, Rth)

Qg: **Gate charge** (allows to calculate the average total gate driver current in function of switching f

$$I_{G(AV)} = Q_G \cdot f_s$$

Gate Driver Design

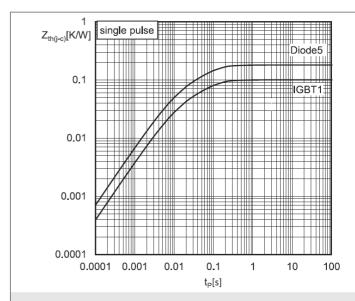

Rth(j-c) MAX: not *very* impacted by TIM (a little bit yes...), only for modules with baseplate

Rth(c-s): strongly dependent by TIM material

#### Rth measure

- Require thermal stability to be measured

- Thermal interference and statistical impacts

| Characte             | ristics                                     |      |       |      |      |

|----------------------|---------------------------------------------|------|-------|------|------|

| Symbol               | Conditions                                  | min. | typ.  | max. | Unit |

| IGBT1                |                                             |      |       |      |      |

| $Q_G$                | V <sub>GE</sub> = -8V+15V                   |      | 1700  |      | nC   |

| R <sub>th(j-c)</sub> | per IGBT                                    |      |       | 0.1  | K/W  |

| R <sub>th(c-s)</sub> | per IGBT (λgrease=0.81 W/(m*K))             |      | 0.077 |      | K/W  |

| R <sub>th(c-s)</sub> | per IGBT, pre-applied phase change material |      | 0.037 |      | K/W  |

Fig. 9: Transient thermal impedance of IGBT1 & Diode5

### Technological Challenges in Power Electronics Silicon devices

manufacturing...

**Alternative way to see**: As we have seen in slide  $64 \ n_i(T) \propto T^{\circ}C$  so intrinsic carrier concentration of silicon increase with temperature  $\rightarrow$  so there is a decrease of the resistance of the semiconductor if T increase! (negative coefficient)

#### All the classic silicon manufacturing challenges

#### negative temperature coefficient risk to cause thermal runaway in case of chip parallelization!

The problem of the Thermal runaway and the temperature coefficient troubles of PN junction

$V_{\text{ON}}$  function of T  $V = \frac{KT}{q} \ln(I/I_s)$  Is  $I_s(T) = I_S(T_1) \cdot 2^{(T-T_1)/10} [A]$

I<sub>s</sub> **double** every 10°C increase of T°K!

$$\frac{dV_D}{dT} \approx -2.2mV/^{\circ}C$$

- If V<sub>On</sub> then PN voltage barrier is lowering

- Ten current flow easier in the diode → I increase → T°K increase!

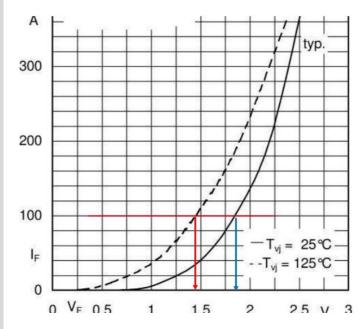

# Consideration on the temperature coefficient vs static losses and parallelization: where is evident in the datasheet?

PN junction has negative temperature coefficient

**Direct Forward PN Junction**

$$V = \frac{KT}{q} ln(I/I_s)$$

Theoretical analysis of PN junction (Si) indicates that Is change by 7% per °C and because 1.07exp10  $\approx$  2 :In other words Is double every +10°C increase. Know Is(T1) Is at T can be calculated with

$$I_S(T) = I_S(T_1) \cdot 2^{(T-T_1)/10}[A]$$

If steady state conditions, increase of temperature cause an increase of Is so Voltage decrease by

$$\frac{dV_D}{dT} \approx -2.2 mV/^{\circ}C$$

In the datasheet the temperature coefficient can be evaluated by analysing the static losses diagram for different temperatures

- Epi diode with negative temperature coefficient

- Good for reducing static losses

- Critical for parallelization

IGBT (or CAL4 diode) and positive temperature coefficient in the nominal range

→ Parallelize is easier!

The design of the intrinsic region (n-), the introduction of implantation, and other techniques can enable power diodes to reverse their temperature coefficient behavior at high currents/voltages from a negative coefficient to positive one.

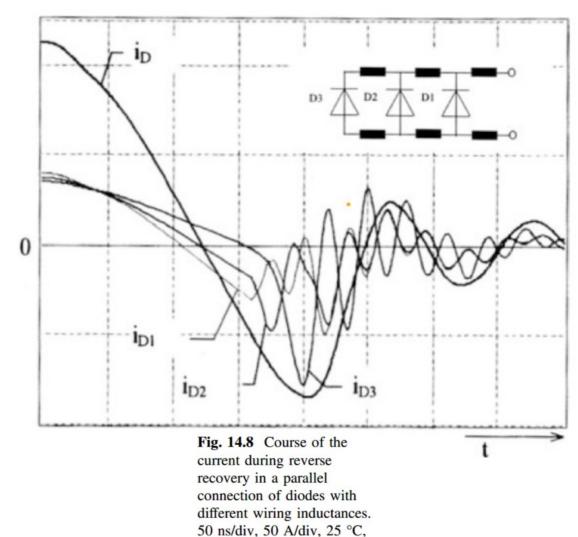

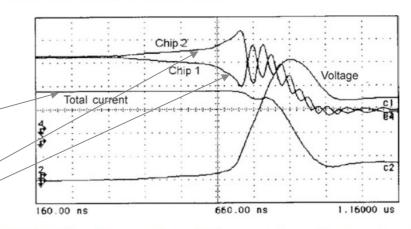

# Turn off Oscillations during reverse recovery in parallel connection of diodes

If a parallel connection is given and oscillations in the reverse recovery of free-wheeling diodes are found, it also has to be investigated whether this is caused by **asymmetrical arrangement of the wirings** and **interconnections**. Oscillations have even been found with a single soft-recovery diode, if the condition is fulfilled that the switching time of the diode  $t_{rr}$  agrees with half the period of the resonance of an LC

In applications with MOSFETs and IGBTs, this can be verified easily: the modification of the gate-resistor RG of the used IGBT or MOSFET can vary the turn-on slope of the transistor and with it the commutation velocity di/dt. So the switching time  $t_{rr}$  of the diode is modified, and in this case the oscillations should vanish.

for **SIC MOSFET** this can be CRITICAL for LAYOUT DESIGN!

$V_{bat}$  approx. 300 V. Figure from [Eld98]

oscillator circuit.

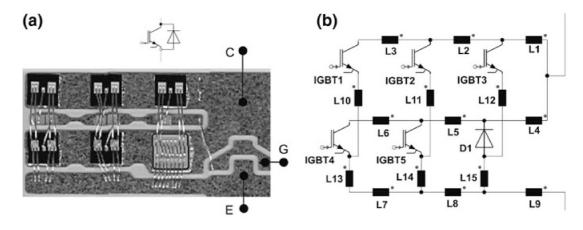

#### Layout chip positioning – trade off – design choiches

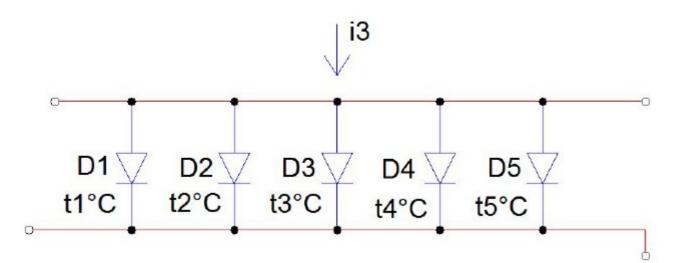

In power modules, often a lot of single dies are connected in parallel.

It is very difficult to give all single dies identical symmetrical conditions in respect to the length of the current-conducting path to the main terminals as well as in respect to the length of the wiring of the drive signals.

Thermal conditions must be considered, too.

Often trade-offs must be made. Figure 11.33 shows an example of parallel connection of five IGBT dies (to form ONE switch with 1 APD FW Diode), in which asymmetric tracks for the main current to the respective die are given.

The wires for the drive signals, for which also a symmetrical setup is of importance, are not drawn in the schematic circuit diagram of 11.33b.

**Fig. 11.33** (a) Realistic power circuit consisting of 5 parallel IGBT chips and one anti-parallel freewheeling diode chip (b) schematic circuit diagram showing the power devices plus the parasitic inductances formed by the current tracks

**Fig. 14.3** Oscillations of the current in two IGBTs connected in parallel. Gate resistors  $6.02~\Omega$  for chip 1 and  $6.45~\Omega$  for chip 2. Current 10 A/div, voltage 50 V/div. Figure according to [Pal99] © 1999 EPE

### **Power Electronics**

6. Power Module Design 2: Simulations

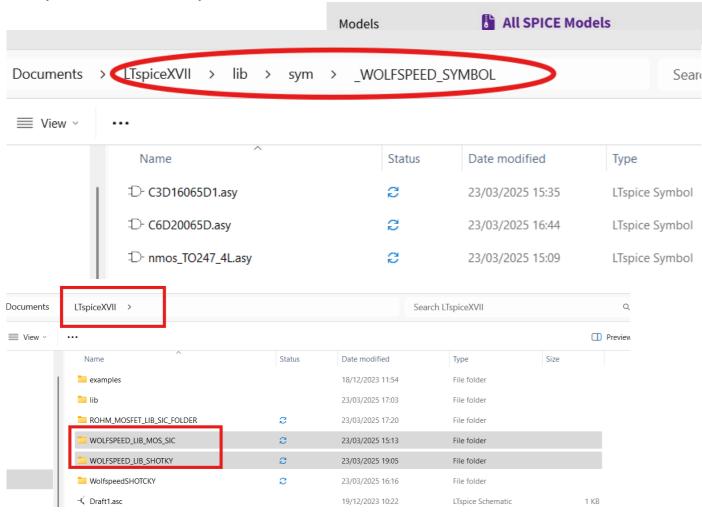

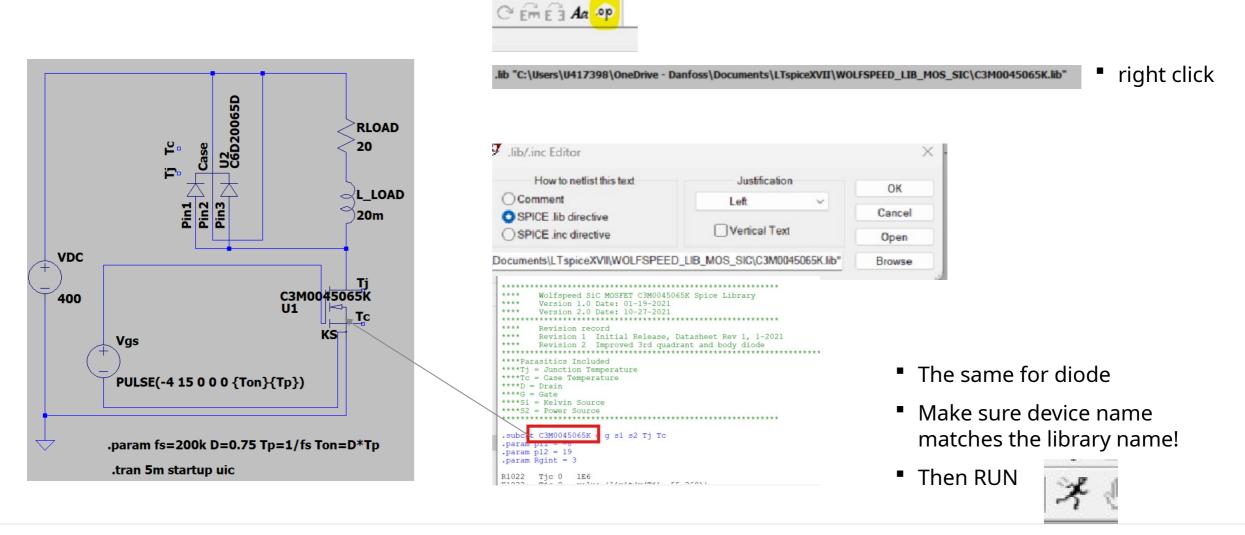

# Simulation example of **DISCRETE** Power Semiconductors: **LTspice Models**

### LTSpice simulations with discrete Power Devices (eg. TO)

Discrete Semiconductors libraries: ex <a href="https://www.wolfspeed.com/tools-and-support/power/ltspice-and-plecs-models/">https://www.wolfspeed.com/tools-and-support/power/ltspice-and-plecs-models/</a>

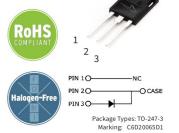

#### C6D20065D1

6th Generation 650 V, 20 A Silicon Carbide Schottky Diode

#### Description

With the performance advantages of a Silicon Carbide (SiC) Schottky Barrier diode, power electronics systems can expect to meet higher efficiency standards than Si-based solutions, while also reaching higher frequencies and power densities. SiC diodes can be easily paralleled to meet various application demands, without concern of thermal runaway. In combination with the reduced cooling requirements and improved thermal performance of SiC products, SiC diodes are able to provide lower overall system costs in a variety of diverse applications.

### LTSpice simulations with discrete Power Devices (eg. TO)

Discrete Semiconductors libraries: ex <a href="https://www.wolfspeed.com/tools-and-support/power/ltspice-and-plecs-models/">https://www.wolfspeed.com/tools-and-support/power/ltspice-and-plecs-models/</a>

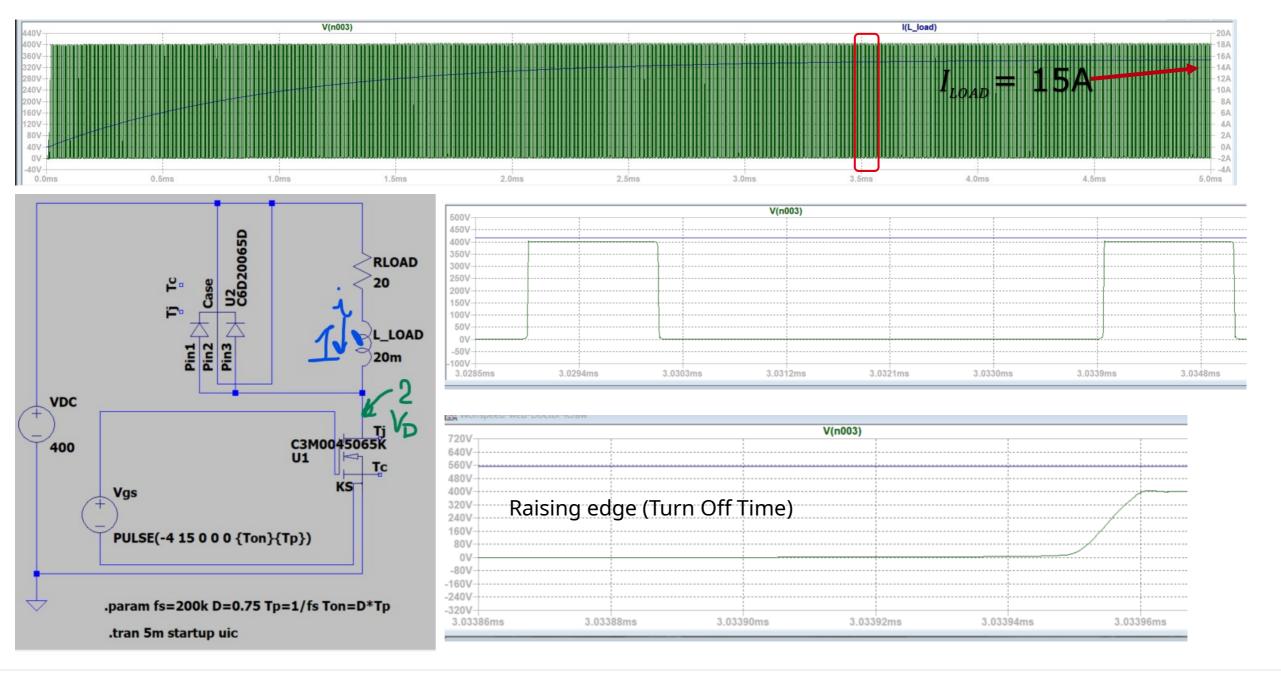

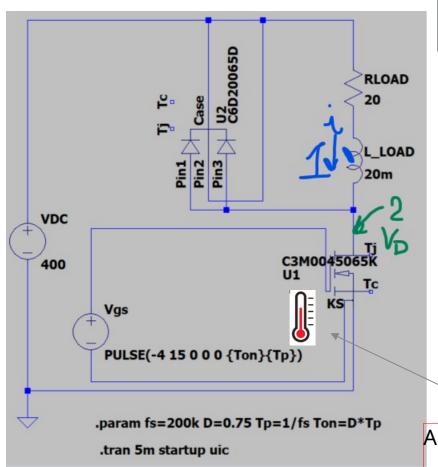

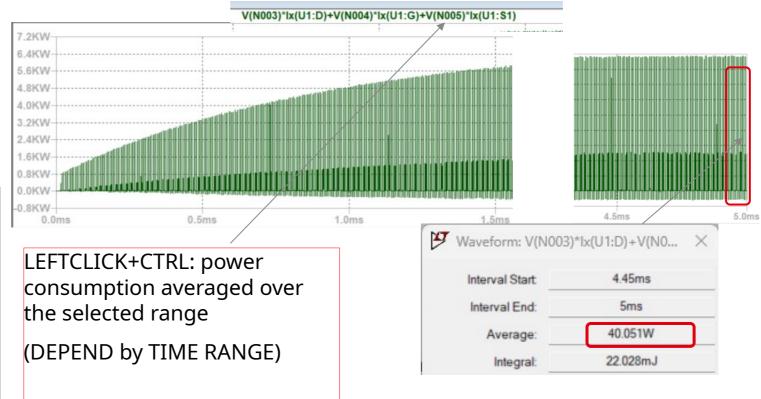

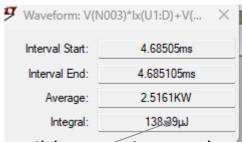

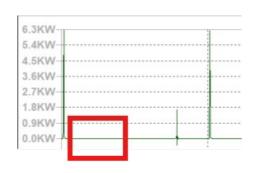

# Dynamic Losses 1/2

**40 Watt** dissipated in the MOS:

a lot?

the **RLOAD** dissipate 400Vx15A  $\rightarrow$  4,5 kW! Only 40Watt dissipated over the power switch (1000 times less!)

ALT+ probe (probe power consumption)

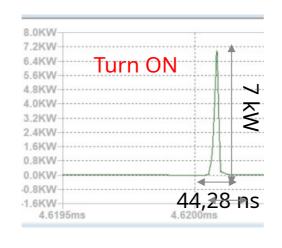

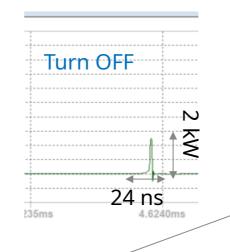

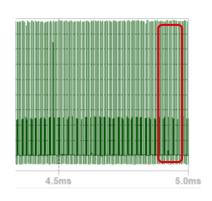

# Dynamic Losses 2/2

possible to estimate also graphically (zoom on Turn on , Left cick + CTRL on title (not very accurate)

$$E_{on} = \frac{44,28 \times 7 \times 10^{-9} \times 10^{3}}{2} = 155\mu J \qquad E_{oFF} = \frac{24 \times 2 \times 10^{-9} \times 10^{3}}{2} = 24\mu J$$

C3M0045065K

Warning: Datasheet Turn ON / OFF calculated differently!

|                                        | <del> </del>     | <del>                                     </del> | <del>                                     </del> |   | +  |                                                                                                          |

|----------------------------------------|------------------|--------------------------------------------------|--------------------------------------------------|---|----|----------------------------------------------------------------------------------------------------------|

| Turn-On Switching Energy (Body Diode)  | E <sub>on</sub>  | _                                                | 57                                               | _ |    | $V_{DS} = 400 \text{ V}, V_{GS} = -4 \text{ V}/15 \text{ V}, I_{D} = 17.6 \text{ A},$                    |

| Turn Off Switching Energy (Body Diode) | E <sub>off</sub> | _                                                | 14                                               | _ | μЈ | $R_{G(ext)} = 2.5 \Omega$ , L= 99 $\mu$ H, T <sub>1</sub> = 175°C<br>FWD = Internal Body Diode of MOSFET |

| /                                      | _                |                                                  |                                                  |   | Ī  |                                                                                                          |

Excercise: explain why this difference from semiconductor's physics concepts

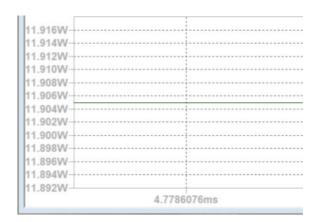

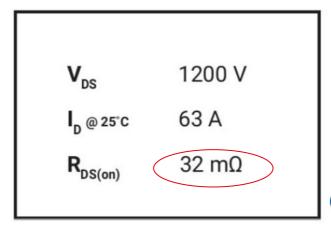

#### Conduction Losses

Need to zoom a lot!  $\rightarrow$  11,9 W

Multiplied by the duty cycle=0.75

$$\rightarrow$$

8,925 W What is  $R_{DS(ON)}$ ?  $\rightarrow$   $W_{on} = V_{on}I_{on} = R_{DS(ON)}I_{on}^2 = 8,925W$

$$I_{LOAD} = 15A$$

$$R_{DS(ON)} = \frac{8,925}{15^2} = \frac{8,925}{225} = 0.039 = 40m\Omega$$

Check datasheet: ok (Typical is +/- 10%)

| Parameter                         | Symbol              | Min.  | Тур. | Max. | Unit | Conditions                                                               | Note                                          |      |

|-----------------------------------|---------------------|-------|------|------|------|--------------------------------------------------------------------------|-----------------------------------------------|------|

| -                                 |                     | !<br> |      | 1    | I    | · · · · · · · · · · · · · · · · · · ·                                    |                                               |      |

| Drain-Source On-State Resistance  | В                   | _     | 45   | 60   | 0    | m0                                                                       | $V_{GS} = 15 \text{ V}, I_D = 17.6 \text{ A}$ | Fig. |

| Drain-Source Oil-State Resistance | R <sub>DS(on)</sub> | _     | 61   | _    | mΩ   | $V_{GS} = 15 \text{ V}, I_D = 17.6 \text{ A}, T_J = 175^{\circ}\text{C}$ | 4, 5, 6                                       |      |

#### Esercizio

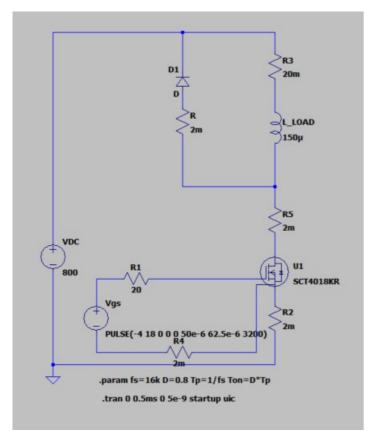

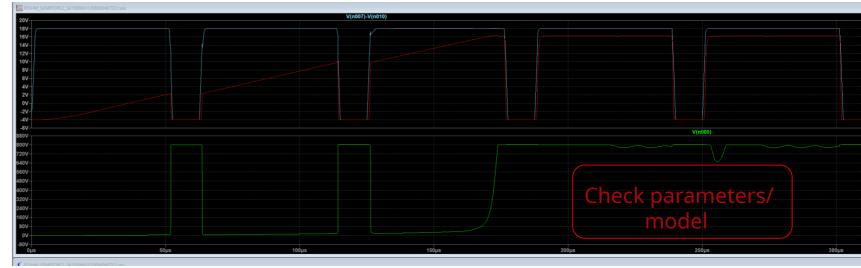

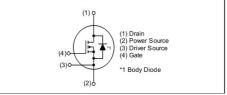

#### SCT4018KR

N-channel SiC power MOSFET

Datasheet

| $V_{DSS}$           | 1200V |

|---------------------|-------|

| $R_{DS(on)}$ (Typ.) | 18mΩ  |

| l <sub>D</sub> *1   | 81A   |

| P <sub>D</sub>      | 312W  |

#### Features

- 1) Low on-resistance

- 2) Fast switching speed

- 3) Fast reverse recovery

- 4) Easy to parallel

- 5) Simple to drive

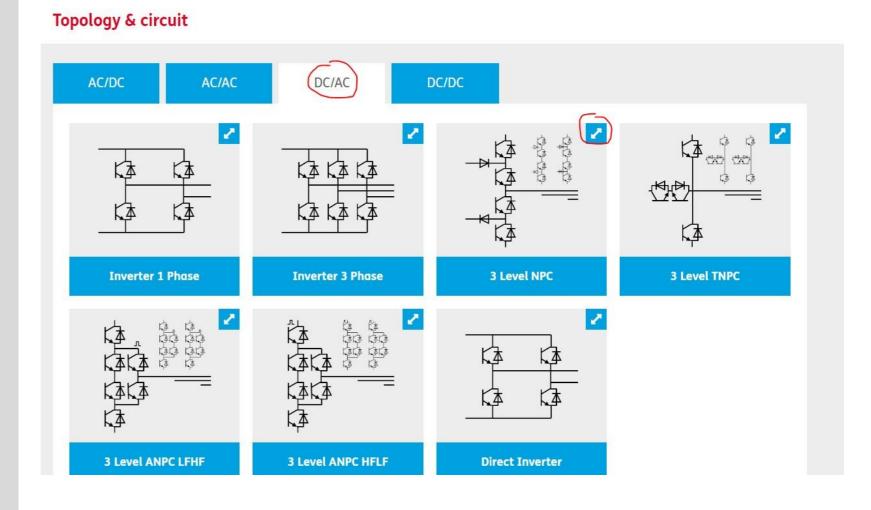

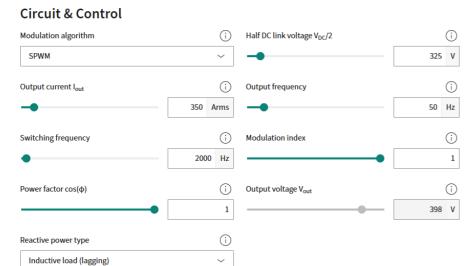

### Simulation example of POWER Semiconductor MODULE SEMISEL

#### Feasibility Details

Immaginiamo che il nostro cliente voglia usare un modulo di potenza come convertitore per applicazioni fotovoltaiche. Alla fine della prima fase di discussione bisognerà quindi avere chiarito

- 1. Il livello di tensione di ingresso

- 2. La corrente media di uscita o RMS (si parla sempre di corrente medie nell'ambito della conversione della energia per grandezze sinusoidali: Il mondo esterno è a 50Hz o 60Hz!)

- 3. Il  $\cos\varphi$  (per applicazioni solari è 1)<sup>3</sup>

- 4. La frequenza della rete di uscita (in USA 60Hz, in Europa 50Hz) : stiamo progettando un convertitore che fornisce una tensione continua dal sistema fotovoltaico e che dovrà allacciarsi su una tensione di rete alternata.

- 5. La frequenza di switching del convertitore (switching frequency) perché come sapete la conversione di energia a semiconduttori si fa con le tecniche di switching.

- 6. La potenza di uscita richiesta (per un modulo di media potenza può essere  $250~\mathrm{kW})$

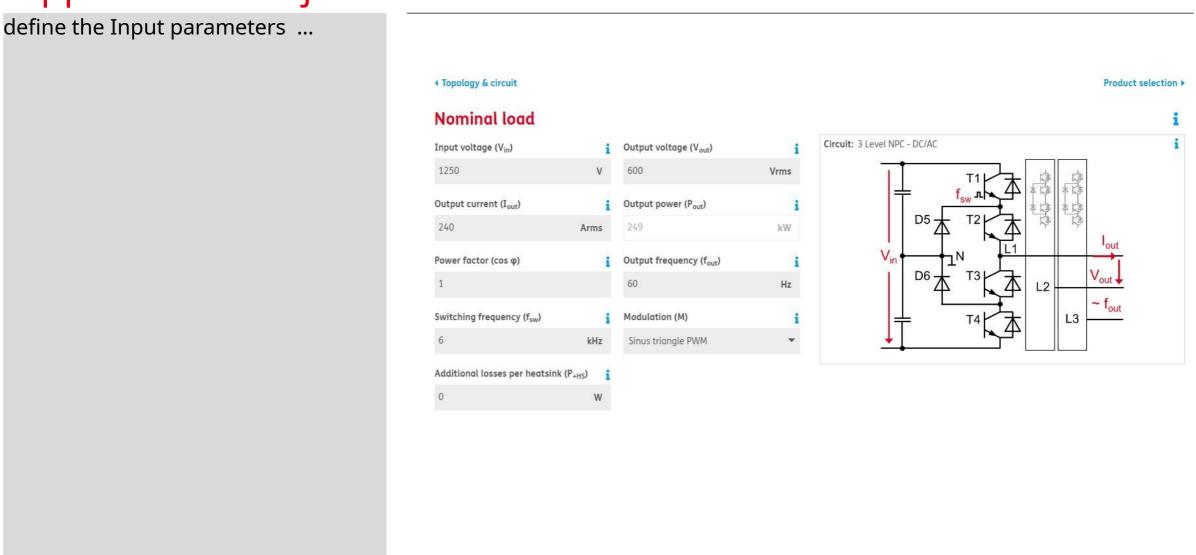

#### 1. Circuit Parameter

DC/AC: 3 Level NPC

#### 1.1 Nominal Load

| Input voltage (Vin)                    | Output voltage (Vout)   |

|----------------------------------------|-------------------------|

| 1250 V                                 | 600 Vrms                |

| Output current (lout)                  | Output power (Pout)     |

| 240 Arms                               | 249.42 kW               |

| cos(φ)                                 | Output frequency (fout) |

| 1                                      | 60 Hz                   |

| Switching frequency (f <sub>SW</sub> ) | Modulation              |

| 6 kHz                                  | Sinus triangle PWM      |

Figura 2.4: Esempio di parametri elettrici per un Modulo di Potenza per applicazioni fotovoltaiche

<sup>3</sup>Questo è un obiettivo. Stiamo progettando un inverter fotovoltaico che deve generare una tensione alternata da immettere in rete e deve convertire quindi la potenza solare in potenza di rete introducendo la più piccola distorsione armonica quindi cercando di riuscire a generare tensioni e correnti perfettamente in fase. Questo perché esistono delle normative entro cui il sistema fotovoltaico può scambiare energia reattiva con la rete e questo non deve essere inferiore a 0.8. Soprattutto perché il distributore valuta (e fattura) la potenza «ATTIVA» prodotta o consumata (e NON quella «reattiva»). Infine quando l'impianto non è attivo (di notte) l'inverter deve comportarsi come un'utenza passiva. Generazione o consumo di energia in impianti solari in ore notturne NON sono permessi

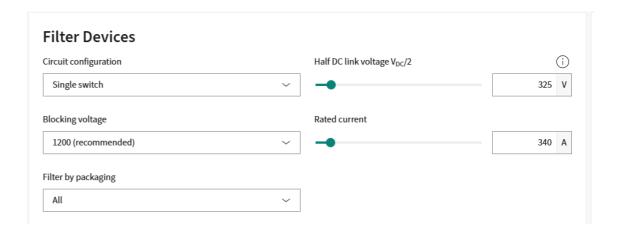

# Example: Design Power Module for Photovoltaic DC/AC application. Project Simulation: SEMISEL 1/7

SemiSel Simulation

Semikron Danfoss

Define the Topology and Circuit...

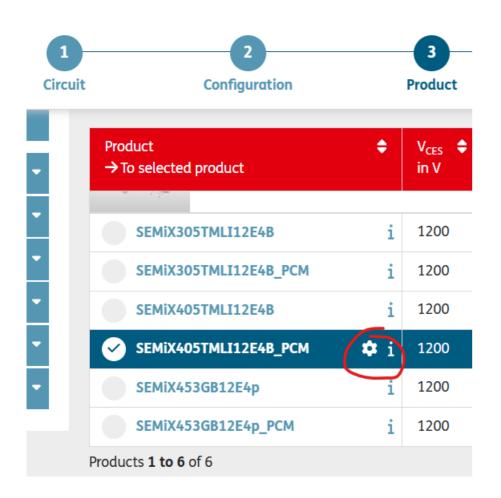

# Example: Design Power Module for Photovoltaic DC/AC application. Project Simulation: SEMISEL 2/7

# Example: Design Power Module for Photovoltaic DC/AC application. Project Simulation: SEMISEL 3/7

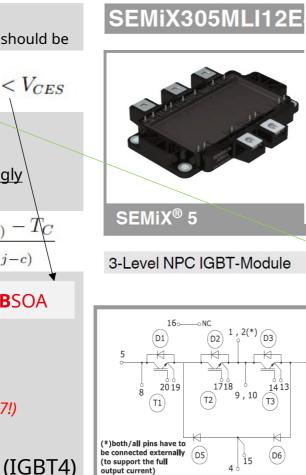

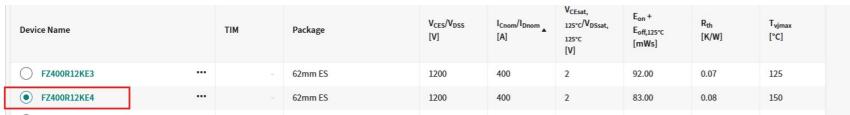

SEMiX305MLI12E4V2 seems to be a module which matches the specifications.

Let's verify if this module work under the specific conditions requested by the application

#### SEMiX305MLI12E4V2

SEMiX® 5

3-Level NPC IGBT-Module

SEMiX305MLI12E4V2

#### Features\*

- Solderless assembling solution with PressFIT signal pins and screw power terminals

- . IGBT 4 Trench Gate Technology

- V<sub>CE(sat)</sub> with positive temperature

| Absolute          | Maximum Rat                                                         | ings                                                  |                 |      |

|-------------------|---------------------------------------------------------------------|-------------------------------------------------------|-----------------|------|

| Symbol            | Conditions                                                          |                                                       | Values          | Unit |

| IGBT1             | '                                                                   | ,                                                     |                 |      |

| V <sub>CES</sub>  | T <sub>j</sub> = 25 °C                                              |                                                       | 1200            | V    |

| Ic                | T <sub>i</sub> = 175 °C                                             | T <sub>c</sub> = 25 °C                                | 451             | Α    |

|                   | 1j = 1/5 °C                                                         | T <sub>c</sub> = 80 °C                                | 347             | Α    |

| Cnom              |                                                                     | '                                                     | 300             | Α    |

| I <sub>CRM</sub>  |                                                                     |                                                       | 900             | Α    |

| V <sub>GES</sub>  |                                                                     | 15-15-21-16-21-17-17-17-17                            | -20 20          | V    |

| t <sub>psc</sub>  | V <sub>CC</sub> = 800 V, V <sub>0</sub><br>V <sub>CES</sub> ≤1200 V | $_{GE} \le 15 \text{ V}, T_j = 150 ^{\circ}\text{C},$ | 10              | μѕ   |

| Tj                |                                                                     |                                                       | -40 <b>17</b> 5 | °C   |

| IGBT2             |                                                                     | *                                                     |                 |      |

| V <sub>CES</sub>  | T <sub>j</sub> = 25 °C                                              |                                                       | 1200            | V    |

| Ic                | T 175 90                                                            | T <sub>c</sub> = 25 °C                                | 453             | Α    |

|                   | T <sub>j</sub> = 175 °C                                             | T <sub>c</sub> = 80 °C                                | 348             | Α    |

| I <sub>Cnom</sub> |                                                                     |                                                       | 300             | Α    |

| ICRM              |                                                                     |                                                       | 900             | Α    |

| V <sub>GES</sub>  |                                                                     |                                                       | -20 20          | V    |

| t <sub>psc</sub>  | $V_{CC} = 800 \text{ V}, V_{CES} \le 1200 \text{ V}$                | $_{GE} \le 15 \text{ V}, T_j = 150 ^{\circ}\text{C},$ | 10              | μѕ   |

| Tj                |                                                                     |                                                       | -40 175         | °C   |

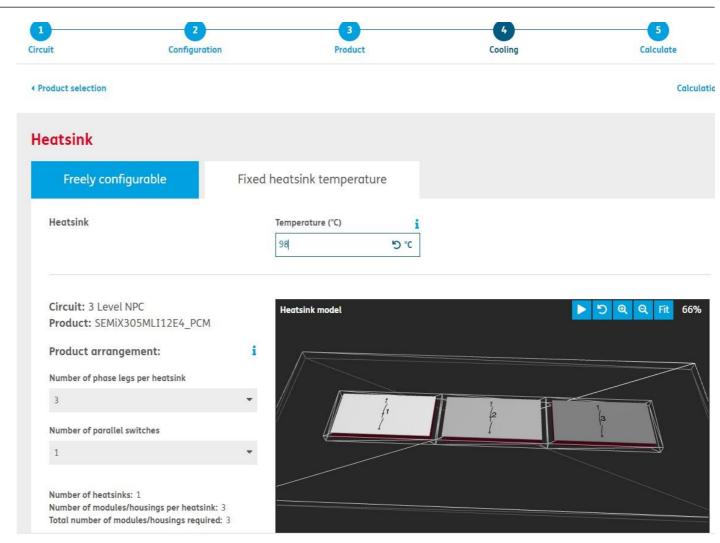

## Example: Design Power Module for Photovoltaic DC/ACapplication. Project Simulation: SEMISEL 4/7

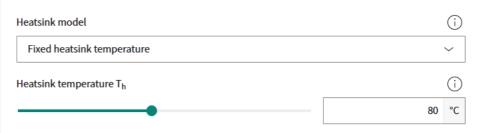

#### Cooling

Once chosen the defined module we must chose the cooling system

For IGBT4 with Tj,op=150°C a possible cooling temperature in stationary state can be 98°C

... based on real (?) case 😊

## Example: Design Power Module for Photovoltaic DC/AC application. Project Simulation: SEMISEL 5/7

#### **Product Selection ...**

- Possibility to customize some key static and dynamic losses for the product selection

- Static losses

$\propto V_{CEO}, T_i$

$R_{th}$ ,  $r_{CE}$

$$I_C\left(T_{case}\right) = \frac{-V_{CE(0)}}{2 \cdot r_{CE}} + \sqrt{\left(\frac{V_{CE(0)}}{2 \cdot r_{CE}}\right)^2 + \frac{T_{Jmax} - T_{case}}{R_{th(j-c)} \cdot r_{CE}}}$$

Thermal Resistances

Dynamic Losses

### Dynamic Losses

| Characteristics     |                                                        |                         |      |      |      |      |  |  |

|---------------------|--------------------------------------------------------|-------------------------|------|------|------|------|--|--|

| Symbol              | Conditions                                             |                         | min. | typ. | max. | Unit |  |  |

| IGBT1               |                                                        |                         | '    |      |      |      |  |  |

| • •                 | 11 200 4                                               |                         | I    |      |      |      |  |  |

| t <sub>d(on)</sub>  | V <sub>CC</sub> = 600 V                                | T <sub>i</sub> = 150 °C |      | 71   |      | ns   |  |  |

| t <sub>r</sub>      | I <sub>C</sub> = 300 A                                 | T <sub>i</sub> = 150 °C |      | 51   |      | ns   |  |  |

| E <sub>on</sub>     | $V_{GE} = +15/-8 \text{ V}$<br>$R_{G,on} = 0.5 \Omega$ | T <sub>j</sub> = 150 °C |      | 17.4 |      | mJ   |  |  |

| t <sub>d(off)</sub> | $R_{G \text{ off}} = 1.5 \Omega$                       | T <sub>j</sub> = 150 °C |      | 488  |      | ns   |  |  |

| t <sub>f</sub>      | $di/dt_{on} = 5700 \text{ A/}\mu\text{s}$              | T <sub>j</sub> = 150 °C |      | 148  |      | ns   |  |  |

| E <sub>off</sub>    | di/dt <sub>off</sub> = 2300 A/μs<br>dv/dt = 3500 V/μs  | T <sub>j</sub> = 150 °C |      | 38.7 |      | mJ   |  |  |

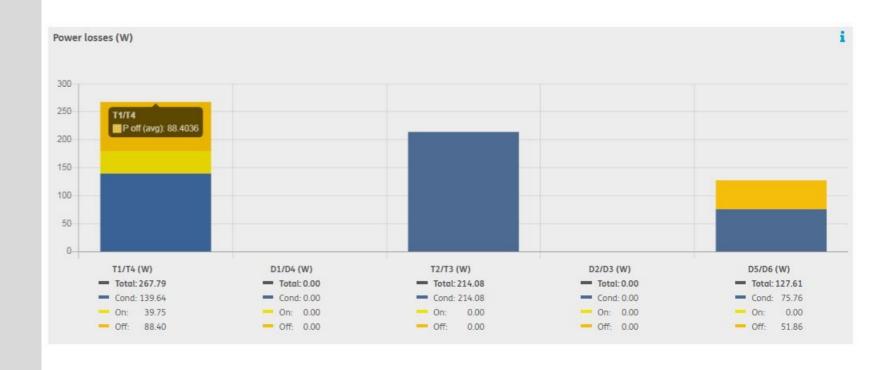

# Example: Design Power Module for Photovoltaic DC/AC application. Project Simulation: SEMISEL 6/7

#### **Simulation outputs**

Junction Temperatures under working conditions

# Example: Design Power Module for Photovoltaic DC/AC application. Project Simulation: SEMISEL 7/7

### Simulation outputs

Power Losses under working conditions

# Datasheet characteristics can be customized (useful for power module comparison)

| Typical values               |            |       |       | Maximum values |       |  |

|------------------------------|------------|-------|-------|----------------|-------|--|

|                              |            | T1/T4 | D1/D4 | T2/T3          | D2/D3 |  |

| I <sub>ref</sub>             | (A)        | 400   | 400   | 400            | 400   |  |

| V <sub>ref</sub>             | (V)        | 300   | 300   | 300            | 300   |  |

| T <sub>j op</sub>            | (°C)       | 150   | 150   | 150            | 150   |  |

| T <sub>j max</sub>           | (°C)       | 175   | 175   | 175            | 175   |  |

| V <sub>f @ 25°C</sub> , Iref | (V)        | (1.8) | (2.2) | 1.59           | 1.39  |  |

| V <sub>f @ Tjop</sub> , Iref | (V)        | 2.2   | 2.15  | 1.75           | 1.38  |  |

| Rg <sub>On</sub>             | (Ohm)      | 2.5   |       | 0.5            |       |  |

| Rg <sub>Off</sub>            | (Ohm)      | 1.5   | 0.5   | 0.5            | 2.5   |  |

| E <sub>on</sub>              | (mJ)       | 21.4  |       | 2.8            |       |  |

| E <sub>off</sub>             | (mJ)       | 29    | 16.4  | 23.9           | 7.8   |  |

| R <sub>th(j-c)</sub>         | (K/W)      | 0.068 | 0.13  | 0/14           | 0.18  |  |

| R <sub>th(c-s)</sub>         | (K/W)      | 0.015 | 0.028 | 0.046          | 0.046 |  |

| R th(c-s) per Moo            | dule (K/W) |       | '     | 0.006          |       |  |

## Semisel exercise: Power Module comparison (facile)

Make a comparison between this module

https://www.semikron-danfoss.com/products/p/semix405tmli12e4b-21919490

https://www.mitsubishielectric.com/semiconductors/powerdevices/datasheets/igbt/t series/cm40 0st-24t e.pdf

1) which type of chips are used for each switch?

hints: for SEMiX5 IGBT look here https://www.infineon.com/cms/en/product/power/igbt/

For SEMiX5 Diode look here:

https://www.semikron-danfoss.com/products/bare-dies/freewheeling-diodes

for Mitsubishi look here: https://www.mitsubishielectric.com

- 2) based on the datasheet of power modules which modules could have bigger chips inside? Explain why you reached these conclusion

- 3) Make a comparison with Semisel of the two modules for a typical UPS application (Input **Voltage: 800Vm Output current 350Arms, Fswitch 5Khz)**

- 4) Explain the difference of the power losses make assumption on the internal chipset and/or other internal packaging/manufacturing dependencies.

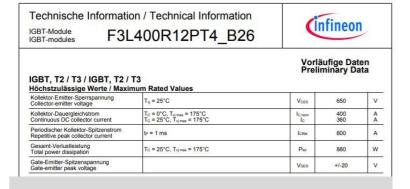

#### SEMiX405TMLI12E4B

<IGBT Modules>

INSULATED TYPE

Semisel exercise2: Power Module comparison (marketing) (difficile)

Make a research on <a href="www.semikron-danfoss.com">www.semikron-danfoss.com</a> website (specifically for SEMITOP CLASSIC, SEMITOP E1 or SEMITOP E2 and find a product which has similar performances on this one (at same voltage ,nominal current and power level)

https://www.infineon.com/dgdl/Infineon-IM06B20AC1-DataSheet-v01\_20-EN.pdf?fileId=8ac78c8c92bcf0b0019368a29d805f6e

- Evaluate the thermal losses based on a typical motor drive application (use 5Khz of switching frequency)

- When the module is convenient for drive application (is there a breakeven for power for instance?): try to make a sort of "fighting guide" (pro/cons DIP-IPM vs Module) based on some technical KPI for power electronics

- Estimate the "cost" to have this product embedded in a servo drive.

#### 650 V TRENCHSTOP™ IGBT7 T7

#### 3.2 Inverter section

| Description                           | Symbol                  | Condition                                                       | Value | Unit |  |

|---------------------------------------|-------------------------|-----------------------------------------------------------------|-------|------|--|

| Max. blocking voltage                 | V <sub>CES</sub>        |                                                                 | 650   | V    |  |

| DC link supply voltage of P-N         | V <sub>PN</sub>         | Applied between P-N                                             | 450   | V    |  |

| DC link supply voltage (surge) of P-N | V <sub>PN (surge)</sub> | Applied between P-N                                             | 500   | V    |  |

| 2                                     |                         | T <sub>C</sub> = 25°C, T <sub>J</sub> < 150°C                   | ±20   |      |  |

| Output current <sup>2</sup>           | lo                      | T <sub>C</sub> = 80°C, T <sub>J</sub> < 150°C                   | ±15   | A    |  |

| Maximum peak output current           | lo (peak)               | T <sub>C</sub> = 25°C, T <sub>J</sub> < 150°C<br>less than 1 ms | ±40   | А    |  |

| Power dissipation per IGBT            | P <sub>tot</sub>        |                                                                 | 32.05 | W    |  |

| Short circuit withstand time          | t <sub>sc</sub>         | V <sub>DC</sub> ≤ 360V, T <sub>J</sub> = 150°C                  | 3     | μs   |  |

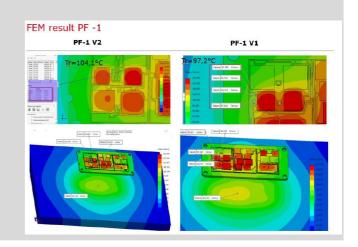

## Customization vs full re-design

- Check if available modules fits the customer application (design effort is zero)

- First level of design: chip customization (reiterate simulation with static and dynamic losses from similar packages)

- If Semisel cannot found a suitable module even with small chip change we need for a full custom design. Critical parameters need to be reviewed

- a. Where losses comes from? Inductances  $\rightarrow$  Over voltages

$$\nabla V = L \cdot \frac{di}{dt}$$

$$\Phi(\overrightarrow{B}) = LI$$

----- → Geometry dependant! → DCB re-layout?

$$L = \mu_0 n^2 l S$$

Temperature heat flow? FEM simulation to evaluate packaging performances?

## Simulation example of POWER Semiconductor MODULE IPOSIM

https://www.infineon.com/design-resources/simulation-modeling/iposim-infineon-power-simulation-tool-plecs

## DC/AC

DC/AC Applications

#### **Thermal**

Confirm / Run  $\, o \,$

## DC/AC

| SWITCH Q1/Q4 | 105.22 °C                     | 246.39 W          | 31.43 W          | 277.81 W     |

|--------------|-------------------------------|-------------------|------------------|--------------|

| DIODE D1/D4  | 80 °C                         | 0.00 W            | 0.00 W           | 0.00 W       |

| SWITCH Q2/Q3 | 84.65 °C                      | 52.9 W            | o W              | 52.9 W       |

| DIODE D2/D3  | 90.38 °C                      | 48.24 W           | 14.09 W          | 62.33 W      |

|              | MAXIMUM JUNCTION  TEMPERATURE | CONDUCTION LOSSES | SWITCHING LOSSES | TOTAL LOSSES |

V<sub>CES</sub> = 1200V I<sub>C nom</sub> = 400A / I<sub>CRM</sub> = 800A

#### 技术信息 / Technical Information

IGBT-模块 IGBT-modules FZ400R12KE4

62mm C-Series 模块 采用第四代沟槽栅/场终止IGBT4和第四代发射极控制二极管

62mm C-Series module with Trench/Fieldstop IGBT4 and Emitter Controlled 4 diode

## Simulation example of POWER Semiconductor **MODULE VINCOSIM**

https://www.vincotech.com/support-and-documents/simulation-software.html

## DC/AC NPC

#### 1. Circuit Parameter

DC/AC: 3 Level NPC

#### 1.1 Nominal Load

| Input voltage (Vin)                    | Output voltage (Vout)   |

|----------------------------------------|-------------------------|

| 1250 V                                 | 600 Vrms                |

| Output current (lout)                  | Output power (Pout)     |

| 240 Arms                               | 249.42 kW               |

| cos(φ)                                 | Output frequency (fout) |

| 1                                      | 60 Hz                   |

| Switching frequency (f <sub>sw</sub> ) | Modulation              |

| 6 kHz                                  | Sinus triangle PWM      |

Figura 2.4: Esempio di parametri elettrici per un Modulo di Potenza per applicazioni fotovoltaiche

| 10-EY122PA005MS-<br>LU39F78T | Samples<br>available | Half-Bridge-<br>NTC | flowDUAL<br>E2 SIC | 1200 | 290 | SIC MOSFET | flow E2 🧿 | 12 | Al <sub>2</sub> O <sub>3</sub> | REQUEST<br>SIMULATION | ☆ |

|------------------------------|----------------------|---------------------|--------------------|------|-----|------------|-----------|----|--------------------------------|-----------------------|---|

|------------------------------|----------------------|---------------------|--------------------|------|-----|------------|-----------|----|--------------------------------|-----------------------|---|

## **Power Electronics**

7. Reliability

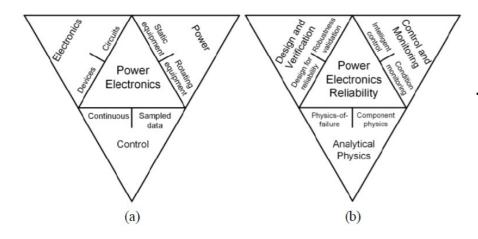

## Design for Reliability

#### THE RELIABILITY CHALLENGE IN INDUSTRY SEEN BEFORE, TODAY AND IN THE FUTURE

|                    | Yesterday                                         | Today                                          | Tomorrow                                                                     |

|--------------------|---------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|

| Customer           | <ul> <li>Replacement if failure</li> </ul>        | Low risk of failure                            | Peace of mind                                                                |

| expectations       | <ul> <li>Years of warranty</li> </ul>             | <ul> <li>Request for maintenance</li> </ul>    | <ul> <li>Predictive maintenance</li> </ul>                                   |

| Reliability target | <ul> <li>Affordable market returns (%)</li> </ul> | Low market return rates                        | ppm market return rates                                                      |

| D&D approach       | <ul> <li>Reliability test</li> </ul>              | - Robustness tests                             | Design for reliability                                                       |

| R&D approach       | <ul> <li>Avoid catastrophes</li> </ul>            | <ul> <li>Improve weakest components</li> </ul> | <ul> <li>Balance with field load / mission profile</li> </ul>                |

|                    | <ul> <li>Product operating and</li> </ul>         | Testing at the limits                          | <ul> <li>Understanding failure mechanisms, field load, root cause</li> </ul> |

| R&D key tools      | function tests                                    |                                                | Multi-domain simulation                                                      |

|                    |                                                   |                                                |                                                                              |

TABLE II

TYPICAL LIFETIME TARGET IN DIFFERENT POWER ELECTRONIC APPLICATIONS

| Applications          | Typical design target of Lifetime             |

|-----------------------|-----------------------------------------------|

| Aircraft              | 24 years (100,000 hours flight operation)     |

| Automotive            | 15 years (10,000 operating hours, 300,000 km) |

| Industry motor drives | 5-20 years (60,000 hours in at full load)     |

| Railway               | 20-30 years (10 hours operation per day)      |

| Wind turbines         | 20 years (24 hours operation per day)         |

| Photovoltaic plants   | 5-30 years (12 hours per day)                 |

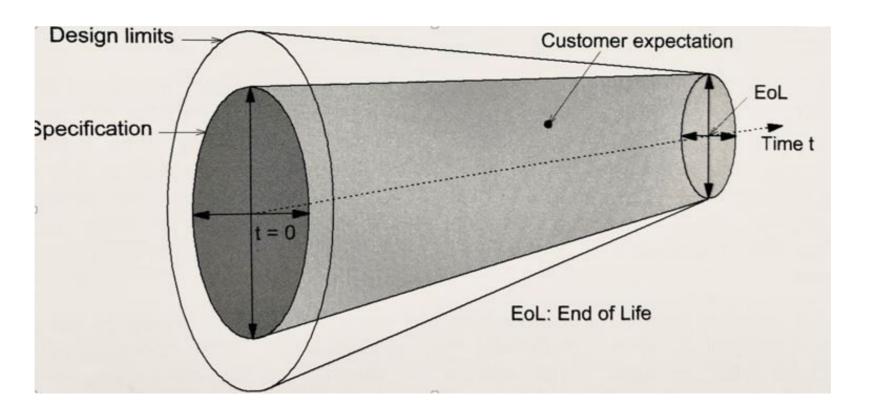

## Design for Reliability: Rimmen Model – Robust Design Process

- "Sudden Failure" (spontaneous, unpredictable): eg a cosmic ray

- "Drift Failures" (predictable, which develop slowly over the time: "fatigue")

## Design for reliability: statistical units and accelerated tests

#### FATILIRE RATE A

N. Of components *Total number of defects* Working time in the field (4.0.2) Failure Rate Failure In Time

$$1FIT = \frac{1}{10^9 h}$$

(4.0.1) #times system fails in 1 / normalized to 109 iours

Eg. n=4, on tot N=8000 devices (sold in the field!) on 5000h

$$\lambda = \frac{4}{8000 \cdot 5000h} = \frac{1}{10^7 h}$$

$\lambda = \frac{10^{-7} h^{-1}}{10^{-9} h^{-1}} = 100 \, FIT$

$$MTBF = \frac{1}{\sum \lambda}$$

$MTBF = \frac{1}{FIT}$  Mean Time Between Failure (4.0.5)

components of the system (chips... wires)

the most defective components dominate the MTBF

$$ppm = \frac{n_{failed}}{n_{delivered}} \cdot 10^6$$

(Field returns, samples excluded)

#### **RELIABILITY – DESIGN FOR RELIABILITY**

Accelerated test law

AF =

$$\frac{t_{op}}{t_{op}}$$

Acceleration Factor Eq. 14.5

Generally, a test can be accelerated if, for example, temperature, voltage, or the rates of change are increased.

Different acceleration models are used, depending on the focus of the test i.e. which failure mechanism is to be examined (Eq. 14.6 to Eq. 14.9). Common to all is that the operating test point (indexed as "stress") is set higher than the target operating point in the later application (indexed as "op"). The tests are performed on a selected number of components in order to validate the electrical, mechanical and thermal parameters as specified in the datasheet. Furthermore, these type tests also serve to determine the test limits of routine tests in the current production.

|                                  | $AF(T) = e^{\left[\gamma\left(\frac{1}{T_{op}} - \frac{1}{T_{Stress}}\right)\right]}$          | Eq. 14.6 |

|----------------------------------|------------------------------------------------------------------------------------------------|----------|

| Arrhenius Model <sup>1</sup>     | $AF(1) = e^{1 \cdot (3p^2 - 3h \cdot 3h$ | -        |

| Eyring Model                     | $AF(U,T) = AF(T) \cdot e^{\left[B \cdot \left[U_{Siress} - U_{op}\right]\right]}$              | Eq. 14.7 |

| Peck Model <sup>2</sup>          | $AF(RH,T) = AF(T) \cdot \left(\frac{RH_{Stress}}{RH_{op}}\right)^{n}$                          | Eq. 14.8 |

| Coffin-Manson Model <sup>3</sup> | $AF(\DeltaT) = \left(\frac{\DeltaT_{Stress}}{\DeltaT_{co}}\right)^{C}$                         | Eq. 14.9 |

Note: FIT depends by Application conditions

temperature of usage and stats observations.

Eg SKIM4 2013-2021  $\rightarrow$  MTBF=  $0,25\cdot 10^8$ ,  $T_{op}=85^{\circ}\mathrm{C}$

## Reliability Requirements and Reliability Tests

$I_{\rm GSS}/I_{\rm GES}$

$I_{\rm DSS}/I_{\rm CES}$

$R_{\rm DS(on)}/V_{\rm CE(sat)}/V_{\rm F}$

$V_{\rm GS(th)}/V_{\rm GE(th)}$

#### **Reliability requirements**

- Temperature and current density increasing

- Severe environmental conditions

- Extension of MTBF for critical applications (automotive...)

#### The needs of "accelerated tests"

- Failure criteria

- Test for **chip qualification** (HTRB, HTGS, H3TRB)

- Test for **Package Stability** (LTS, HTS, TC, PC)

- Test for mechanical integrity (V, MS)

#### **Failure Criteria**

|                | Name                                                                | Conditions                                                                                                                                                                                                                                                                              | Standards            |

|----------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| HTRB           | High temperature<br>reverse bias test <sup>a</sup>                  | MOS/IGBT: 1000 h, $T_{\text{vjmax}}$ , $V_{\text{CEmax}} (\leq 2.0 \text{ kV})$ , $0.8 \times V_{\text{CEmax}} (> 2.0 \text{ kV})$                                                                                                                                                      | IEC60747-9:1998      |

|                |                                                                     | Conv: 1000 h, $T_j = 125^{\circ}\text{C}$ ,<br>$V_{\text{RM}} = 0.9 \times V_{\text{RRM}}$ ,<br>$V_{\text{RM}}/V_{\text{DM}} = 0.8 \times V_{\text{RRM}}/V_{\text{DRM}}^{\circ}$                                                                                                        | IEC 60747-2/6 Kap. V |

| HTGS<br>(HTGB) | High temperature<br>gate stress test <sup>a</sup>                   | $1000 \text{ h}, \pm V_{\text{GEmax}}, T_j = 125^{\circ}\text{C}$                                                                                                                                                                                                                       | IEC60747-9:1998      |

| H3TRB<br>(THB) | High humidity<br>high temperature<br>reverse bias test <sup>a</sup> | 1000 h, 85°C, 85% RH,<br>$V_{CE} = 0.8 \times V_{CEmax}$ ; however,<br>max . 80 V, V <sub>GE</sub> = 0 V                                                                                                                                                                                | IEC60749:1996        |

| LTS            | Low temperature<br>storage test <sup>b</sup>                        | $T = T_{\text{stgmin}}, 1000 \text{h}$                                                                                                                                                                                                                                                  | IEC60068-2-1         |

| HTS            | High temperature<br>storage test <sup>b</sup>                       | $T = T_{\text{stgmax}}, 1000 \text{h}$                                                                                                                                                                                                                                                  | IEC60068-2-2         |

| TST            | Thermal shock <sup>a</sup>                                          | $T_{\text{stgmin}} - T_{\text{stgmax}}$ ; $-40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ , but $\Delta T_{\text{max}} \leq 165 \text{ K}$ $T_{\text{storage}} \geq 1 \text{ h}$ $T_{\text{change}} \leq 30 \text{ s}$ High power, standard: 20 cycles High power, traction: 100 cycles | IEC60749:1996        |

|                |                                                                     | Medium power: 50 cycles<br>Conv.: 25 cycles <sup>c</sup>                                                                                                                                                                                                                                |                      |

+100% USL

+ 100% USL

+ 20% IMV + 20% USL

- 20% LSL

+ 20% IMV

| Conv.: 25 | ower: 50 cycles<br>cycles <sup>c</sup> |                      |

|-----------|----------------------------------------|----------------------|

| 9(2001)   |                                        | (a) Infineon, (b) SD |

TC

PC

PC

V

MS

Name

cyclinga

Temperature

cyclingb

Power cyclinga

Power cyclingb

Mechanical shock

Vibration

Conditions

External heating and cooling

$2 \min . < t_{\text{cycl.}} < 6 \min;$  $\Delta T_{\rm C} = 80 \, \rm K$  $T_{\rm cmin} = 5^{\circ}{\rm C}$

Conv.: 5000 cycles<sup>c</sup>

$T_{\rm change} \leq 30 \, \rm s$  $T_{\text{stgmin}} - T_{\text{stgmax}}$ : 100 cycles Conv. modules: 25 cycles<sup>c</sup>

cooling

Two-chamber air system,

Internal heating and external

$0.5 < T_{\rm cycl} < 10 \, \rm s; \, \Delta T_{\rm i} = 60 \, \rm K$

$T_{\text{imax}} = 125^{\circ}\text{C}, 130,000 \text{ cycles}$

Internal heating and external

$\Delta T_{\rm i} = 100 \text{ K}, 20,000 \text{ cycles}$ Conv. modules: 10,000 cycles<sup>c</sup>

Half-sine pulse, 30 g, three times

High power, standard: 2000 cycles Medium power: 5000 cycles

Standards

IEC60747-9:1998

IEC60747-2/6 Kap. IV

IEC60068-2-14 Test Na

IEC60747-9:1998

IEC60749-34

IEC60068-2-27 Test Ea

Sinusoidal sweep: 5 g, 2 h per axis IEC60068-2-6 Test Fc

$R_{\text{th}(j-c)}/R_{\text{th}(j-s)}$ Not below specification limit VISOL USL, upper specification limit: LSL, lower specification limit: IMV.

**IMV**: Initial Measured Value

## Reliability Tests: HTRB (chip qualification)

- Tested in Inverse, and close to Tj,op

- Long term current losses stability

- Residual of the production process can impact this test

- Leakage current constant monitoring

- Examples of 8 DUTS and failure after 900 hours

- Residual and contamination could increase the accumulation of mobile ions which could cause passivation degradation of the junction and leakage increase.

- Possible to detect also tome design defect of the package

## Reliability Tests: HTGS (chip qualification)

- Monitor the IGBT or MOS current gate current losses stability (max limited to ±20V)

- Thin dioxide surface of 100 nm generate intense Electric field through the gate oxide (2MV/cm! even at few volts like ±20V)

- Gate oxide must be defect free (otherwise Tunnel Effect is facilitated!) and only low surface carriers' density is acceptable

- Test is accelerated by increasing the max T<sub>jop</sub>

- As the losses current trough the oxide are very small (< 10nA) the test is very sensible to eventual contaminations (thermocouples+glue perturbation increase gate losses for instances!)</p>

- Possible cause of failure is production residuals (glue solvents... etc...)

- So this test is also important to verify the cleanliness of the chip surface during assembly

## THB (H3(V,T°C,Hum)TRB or HV-H3TRB) (chip qualif)

- This test evaluate the impact of the impact of the humidity on the long term performances.

- Perfect sealing is not possible (and even unwanted for the condensation creation or for high linear coefficient expansion of the silgel)

- Silgel/soft mould can be penetrated by water ions accelerated by high electrical field.

- The test target is to detect weak points of the chip passivation or process contaminations.

- The current target is 80% of maximum voltage limited to 80V but new chip technology allow to go beyond this limit (from H3TRB to HV-H3TRB which is mandatory requirement for Solar application for instances)

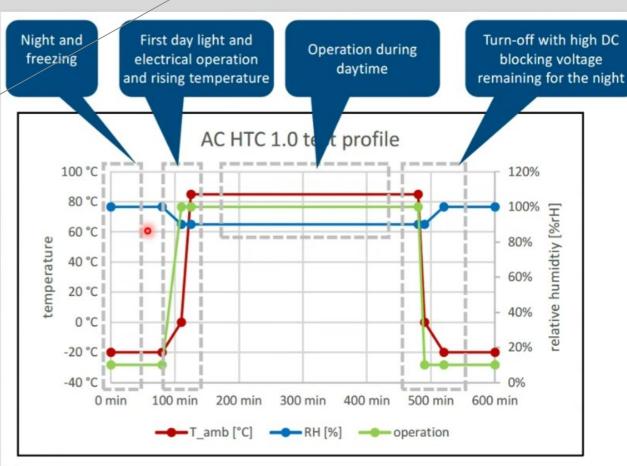

- Possible to enhance the stress of the HVH3TRB during switching conditions, the so-called "climatic test under operation" (see after: for PV system need to simulate the night/day transient, and also static inverse operation is not realistic in real operations!)

- The impact of second soldering...

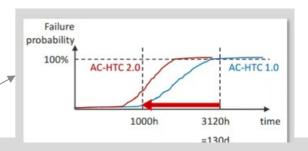

## **AC-HTC**

#### **Alternating Current – Humidity Temperature Cycling**

| Test    | Conditions                                                       | time   | Comments                                                                                               |

|---------|------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------|

| HTRB    | T = Tvj,max; Vgs = 0V;<br>Vds=80%100% Vnom                       | 1000h  | No humidity                                                                                            |

| H3TRB   | T = 85°C; rH=85% Vgs = 0V;<br>Vds=80V                            | 1000h  | Very low voltage level                                                                                 |

| HVH3TRB | T = 85°C; rH=85% Vgs = 0V;<br>Vds=80% Vnom                       | 1000h  | Harsher and more realistic requirements then H3TRB                                                     |

| AC-HTC  | T = -20°C85°C;<br>rH=85100%;<br>Vds=66% Vnom<br>Active operation | >3000h | Even more realistic to PV<br>field scenario than<br>HVH3TRB and reproducing<br>specific field failures |

#### background

- Findings in humidity robustness of early SiC devices in 2010

- Under standardization?

# Reliability Tests: HTS LTS High/Low Temperature STORAGE (Package Qualification)

- Target is to verify plastic materials integrity over life time.

- To be intended as **NON operative temperature** limit for assembled Power Module (it is NOT a storage limit of not-assembled modules...)

- Soft mould can have degradation at temperatures higher than 180°C.

- Low temperature is critical for plastic materials and they lose elastic capabilities.

- The same the silicon soft gel "cracks" at temperatures below -55°C.

- Non operative storage limits for power modules are typically -40°C / +125°C.

- New application require this range to be extended: this will generate more challenges for this test in future.

## Reliability Tests: TC and TS (1/2) (Package qualification)

- Temperature Cycling → temperature (from <u>EXTERNAL</u> sources) change rate between 10°C and 40°C in one minute. No Voltage (the temperature is changed by external sources)

- Temperature Shock → Temperature changes in rate below than 1 min (air chamber with elevator, or if faster with liquid to liquid: warm oil and liquid nitrogen: not for power modules, YES for DBCs)

- Need to reach the temperature equilibrium after the change (between 30 minutes and 2 hours)

- The definition "temperature cycling" can be slightly different from different power module manufacturers

- The test simulate the temperature change from external sources → the DUT is not under operation!

## Reliability Tests: TC and TS (2/2)

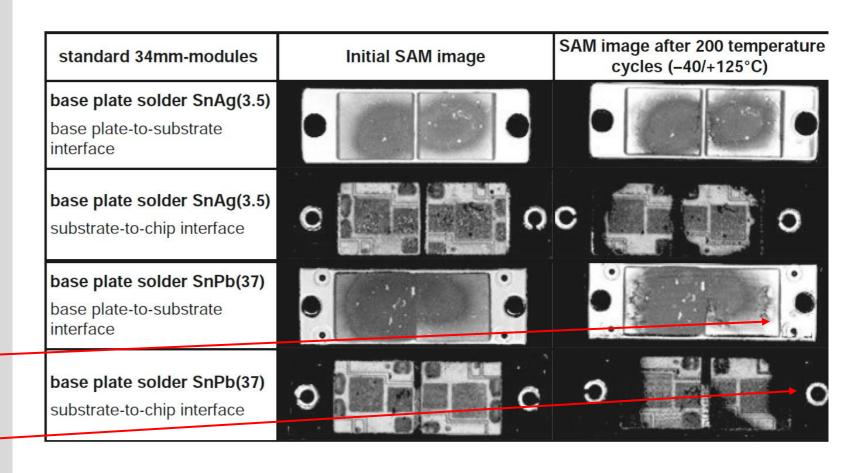

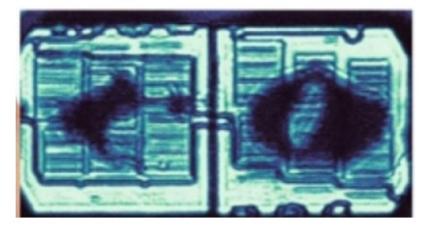

This test cause mechanical stress on materials with different thermal expansion coefficients and the effect can be evaluated by delamination or cracks on the copper/Al2O3 layers with SAM analysis

Here two solder materials are evaluated on module with 34mm baseplate. Standard SnPb(37) after 200 thermal cycles from -40°C to 125°C performed with two air chamber show more "white" areas (high acoustic reflexion) due delamination which absorbs the acoustic wave). Black areas indicate absence of acoustic reflection because delamination(\*)

(\*) SAM signal it sent from baseplate surface , closer reflections reduce the power signal which does not penetrate the deeper layer

## Conventional SAM vs Laser (Optical) Microphone based SAM

- Conventional SAM has better resolution vs X-Ray for detecting voids between baseplate and DCBs

- Conventional SAM need mechanical parts and the microphone to interface acoustic signals received by reflection and transformation to electrical signals to be analyzed in post-processing.

- New technologies<sup>(1)</sup> make usages of laser microphones (or optical microphones): based on principle that *sounds impact speed of light!*

- Photo-Acoustic imaging: Fabry-Perot Interferometer. Acoustic pressure modify the air refraction index. This change the optical wave-length of the light transmission. No mechanical parts needed → faster

- Much better resolution and sensibility of X-Ray (good for in-line mass production test) but still not able to detect small cracks (so for postprocessing analysis after thermal cycling reliability test still conventional SAM is better)

Solder voids detected by C-SAM

Solder voids detected by laser microphone

#### (1) XARION, <a href="https://xarion.com/en/technology/technology">https://xarion.com/en/technology/technology</a>

Balthsar Fischer, Optical microphone hears ultrasounds, Nature Photonics, June 2016, Vol 10 N.6

Preißer S., Fischer B. and Panzer N., Listening to Ultrasound with a Laser, Optik & Photonik Volume12, Issue5, Dec 2017

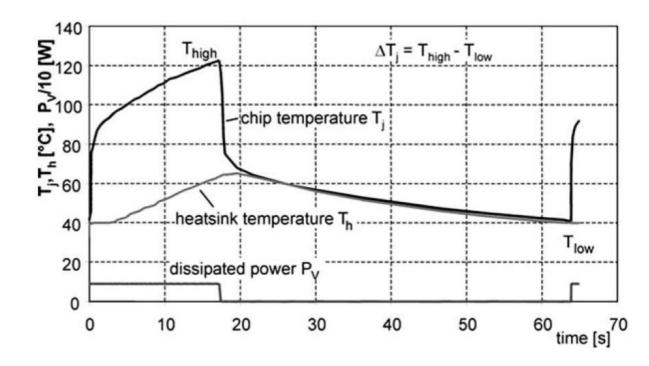

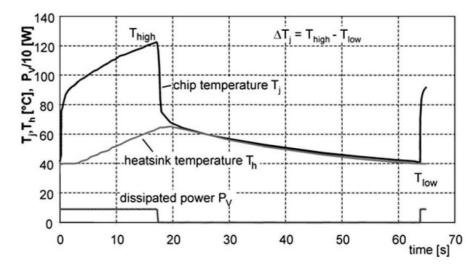

## Package Stability: Reliability Tests: PC (1/4)

- Power Cycling is performed with <u>active chip</u> which warm the module with the electric dissipation during cyclic switch on and switch off

- This test target the chip power losses mounted on a specific modules, so it is key to qualify the chip itself working on a specific package.

- The smaller is the chip the more challenge is this test as power dissipation is more critical

- DUT is mounted on heatsink under nominal working condition. After reaching of Tvj,max the DUT is switch off and cool down is started

- When Tmin is reached the current is switch on again and the cycle restart.

- A significant temperature gradient is generated during the test

Example of Power Cycling test and temperature shape during the cycling

## Reliability Tests: PC (2/4)

• Heatsink temperature is used for control purpose.

Typical PC parameter is picture

$$\nabla T_j = T_{high} - T_{low}$$

n the

Another key parameter is

$$T_m = T_{low} + \frac{T_{high} - T_{low}}{2}$$

- Longer temperature cycle represents higher stress

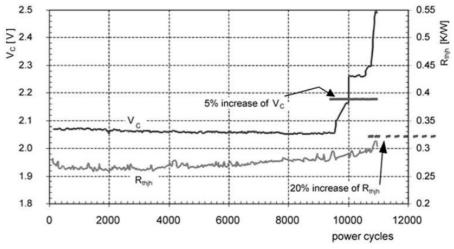

- This thermal stress leads to the generation of fatigue marks on materials which can he highlighted by the increase of forward Voltage which is constantly monitored

- Thermal resistance (Rth-jh initial value is measured with the

- Rth NOT steady state

$$R_{th(a-b)} = \frac{T_a - T_b}{P_V} = \frac{\nabla T}{P_V}$$

Rthjh increasing during the test cause also an increase of the Vc which is typical indication of the reached limit of PC (in this case after 90k cycles)

## Reliability Tests: PC (3/4)

- A first 5% VC increase can be an indication of bond wire lift off.

- This cause further increase of the resistance and further static losses till the bond wire damaging

- This cause the reaching of EOL

#### Failure conditions for the PC tests

- VC increase from 5% to 20% depending by measure accuracy. First step is due to bond wire lift off.

- Rth increase beyond the 20% values "measured" at the starting of the test (this is NOT the Rth indicated in DS which is STEADY STATE! But for comparison purpose is ok to use this measure)

- Failure of typical device characteristics (f.i blocking capability or gate emitter isolation capacity

## Reliability Tests: PC (4/4)

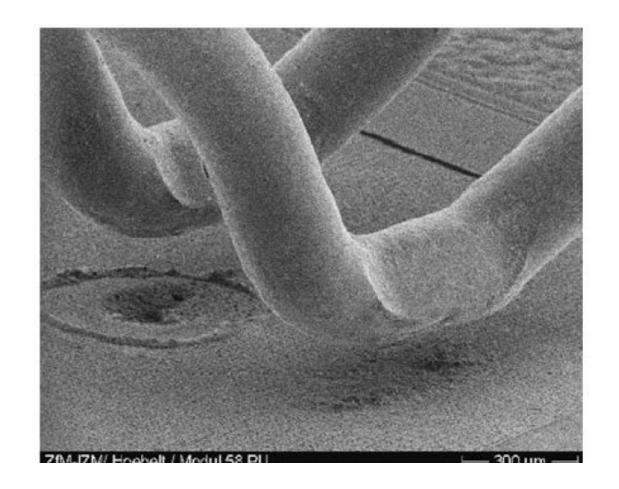

Bottle-neck during power cycling is often the wire-bond. But especially for "small" chips this could not be the case and also the chip surface can generate failure mechanism

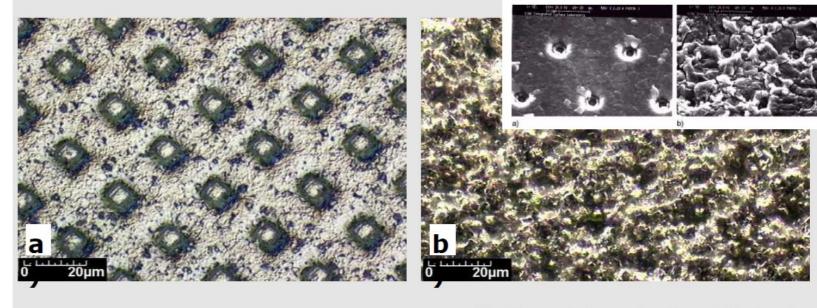

### Recostruction of Al chip surface (Power Cycling)

a) Microscopic image of emitter metallization of chip from phase not cycled (cell structure clearly visible)

**b)** Microscopic image of emitter metallization of failed chip after power cycling test (cell structure not visible)

Failure mechanism of power cycling

→ Destruction of chip metallization

## Reliability test limits depend by the application!

Motor drive: 100Kcycles (elevator

OTIS!)

UPS, Solar: 15kpcs is ok!

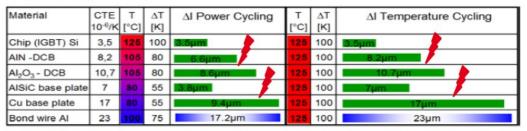

PC and TC stress require CTE similar for different materials.

SiC life times is 1/3 of IGBT (Ok for Solar and UPS where efficiency is the key parameter. Not OK where PC 100Kcycles is required)

Design strategy to increase the PC/TC level

- Removing Baseplate

- Sinter technology

#### Stress!

Example: Length L = 1cm; dT=100K

Figure 2.7.9 Linear expansion of different material layers in a power semiconductor module with an assumed edge length of 1 cm. Left: for a temperature gradient in the module as for a typical power cycle; right: for heating up the entire module as for temperature cycling with identical

#### Sinter-Technology: removing of chip solder joint

| material                               | CTE<br>10-6/K | T<br>[°C] | QT<br>[K] | dL Temperature Cycling |

|----------------------------------------|---------------|-----------|-----------|------------------------|

| die (IGBT)                             | 4             | 125       | 100       | M4/1/Jumil             |

| Ceramic AIN                            | 4,4           | 125       | 100       | 147µm                  |

| Ceramic Al <sub>2</sub> O <sub>3</sub> | 8,3           | 125       | 100       | 8,3µm                  |

| <del>Perspiate</del>                   | 47            | 105       | 400       | - Addison              |

| Bond wire* Al                          | 23            | 125       | 100       | 23µm*                  |

Stress does not disappear, but sinter layer is able to handle the stress!

## Reliability: Challenges for the Future

#### **H2S requirements**

**HALT** test

#### **Mission Profile**

#### **Challenges for the Future**

- Current density continuously increase and silicon area decreasing

- Power density

- PC test for wideband gap material (SiC, GaN)...

- Switching frequency increase ad Stray Inductance limits

- Efficient way to drain heating

- HVH3TRB more than 2000 hours, H2S ...

## **Power Electronics**

8: Emerging applications in power electronics based on Silicon Carbide and Gallium Nitride

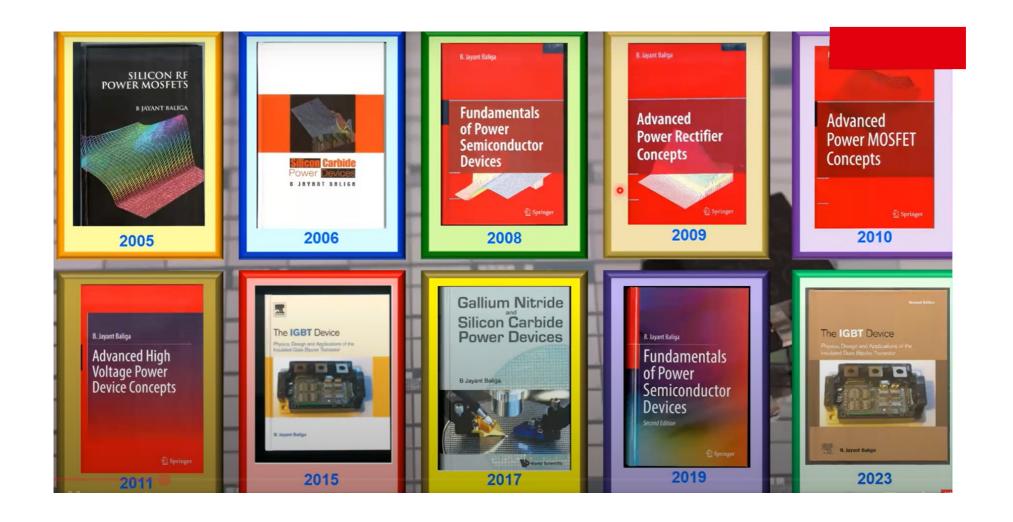

#### Wide Band Semicondutcors Power Devices

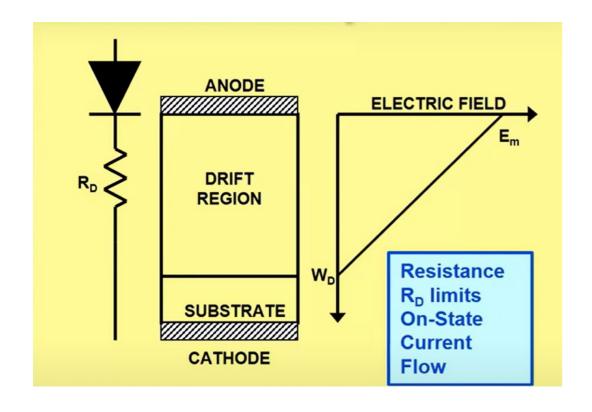

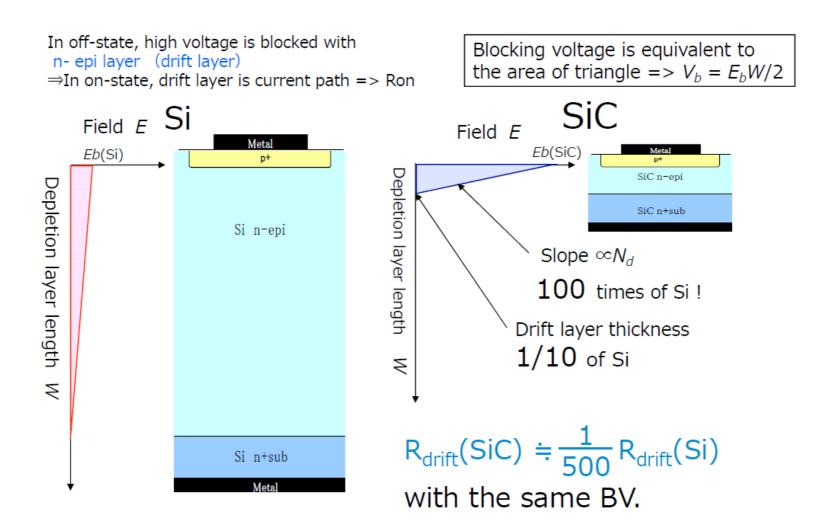

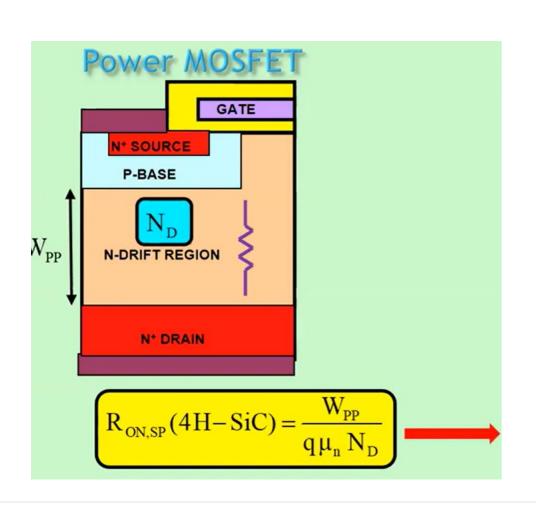

$$R_{ON,SP} = \frac{4BV^2}{\epsilon_S \mu_n E_G^3} \Rightarrow \frac{4BV^2}{\epsilon_S \mu_n E_C^3}$$

Baliga's Figure of Merit (BFOM) for Power Semiconductor Devices:

BFOM =

$$\varepsilon_{\rm S} \, \mu_{\rm n} \, E_{\rm C}^3 = \frac{4 \, BV^2}{R_{\rm ON,SP}}$$

Goal: Low On-State Power Loss

Rif: , **J. Balyga** *My Quest for the Ideal Power Switch*, NC State ECE Lecture 09/2023

https://www.youtube.com/watch?v=mDnOyzMpu1s&t=22s

#### Overview

Strong covalent bonds between Si and C make SiC extremely hard, chemically inert and with high thermal conductivity

It has wider "forbidden" band gap, so more difficult to bring electron from the valence band to the free electron state (conduction band) and is more difficult to have "impact" ionization

Silicon  $T_{jmax}$ =150°C. After T> $T_{jmax}$   $n_i$  inside p-type (or  $p_i$  inside n-type) start becoming preponderant and p-n junction inverse polarized loses his isolating characteristics

[Ec-Ev](SiC)>>[Ec-Ev](Si)  $\rightarrow$  Tjmax SiC 200°C theoretically up to 1000°C.

Corollary→ SiC easy to develop cooling system (smaller)

Note: Power Cycling bottle neck often due to "surrounding" materials not to SiC! (less bond wires as SiC chips smaller, plastic, CTE...

"Baliga Figure of Merits" linked to the semiconductor properties

$$n_i^2 = N_c N_v \exp\left(\frac{-E_g}{kT}\right)$$

$$R_{ON} = \frac{4V_{BD}^2}{\varepsilon_s \mu_n E_C^3}$$

BFOM =

$$\epsilon_s \mu_n E_C^3$$

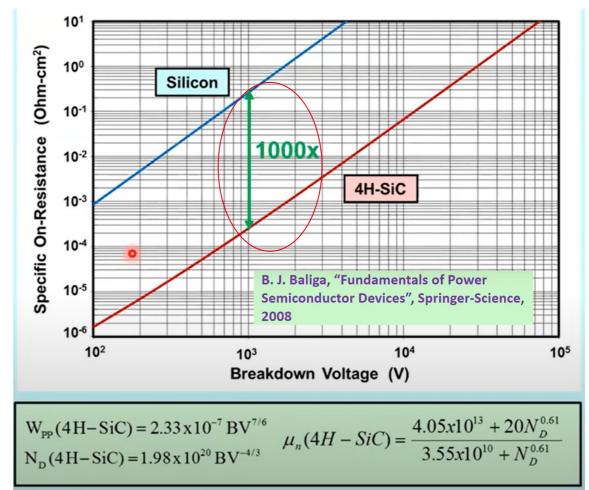

## Figure of Merit (BFOM) comparison SiC vs Si and R<sub>oN</sub>

Hexagonal, 4 bistrateRamsdell notation

SiC  $R_{ON}$  << Si  $R_{ON}$  because the material characteristics

$$R_{ON} = \frac{4V_{BD}^2}{\varepsilon_s \mu_n E_C^3} - \text{Critic BrD El}$$

SiC enable much higher performances than Silicon

SiC MOS usually can have higher Voltage BD level (reason why Si MOS does not exist at 1200V and at parity of voltage shows much higher  $R_{ON}$ )

R<sub>ON</sub> key DS characteristics

|                                                 | Si             | GaAs             | 4H-SiC          | GaN             |

|-------------------------------------------------|----------------|------------------|-----------------|-----------------|

| BFOM = $\epsilon_s \mu_n E_C^3$                 | 1              | 17               | 119             | 537             |

| (normalized to Si)                              |                |                  |                 |                 |

| Bandgap (eV)                                    | 1.11           | 1.43             | 3.26            | 3.5             |

| Breakdown Electric Field (V/cm)                 | $3 \cdot 10^5$ | $3.5 \cdot 10^5$ | $35 \cdot 10^5$ | $35 \cdot 10^5$ |

| Electron mobility $\mu_n \ (cm^2/Vs)$ at $300K$ | 1350           | 6000             | 800             | 1200            |

| Relative dielectric constant $\epsilon_s$       | 11.8           | 12.8             | 9.7             | 9               |

Silicon Carbide Power MOSFET C3M MOSFET Technology

CREE \$

### Comparison MOS Unipolar SI vs MOS Unipolar SiC (not in scale)

# Power SiC MOSFET: R<sub>ds\_ON</sub> vs Silicon

#### **Market Tends**

TRANSFORM: Trusted European SiC Value Chain for a Greener Economy

Complete EU supply chain from silicon wafer to system demonstrators

Supply chain critical (pandemy, geopolitical situation) but also EU SiC gap vs US/Japan

New factory 8 inches SiC STM started

### Advanced SiC Manufacturing Technology

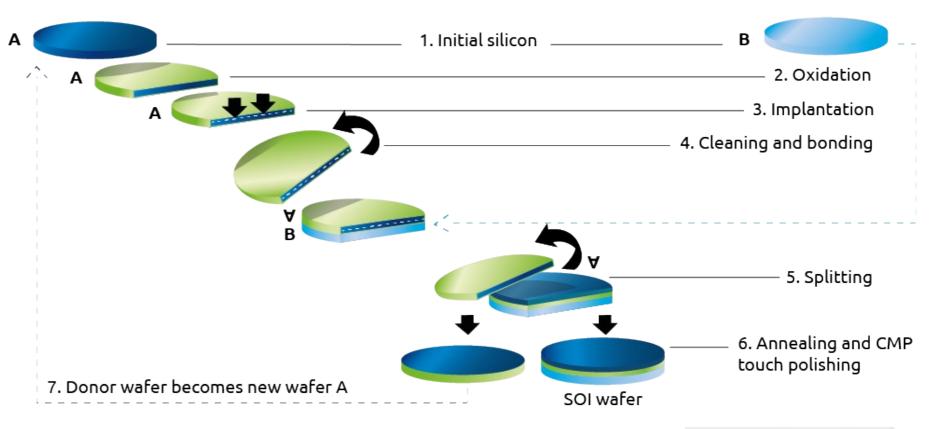

- SiC with conventional manufacturing of single crystal ingots: 2400°C (vs 1500°C for Si)

- Time: several weeks for growth (vs some days for growing time in Si)

- Smart-Cut idea: growth single crystal wafer on poly-silicon wafers and re-usage

### Application landscape

SiC and GaN not new! Already known

- GaN: High frequency, RF, satellites where €/A is never a problem (Power Electronics → commodities → cost is a bigger KPI). GaN: widely used in optoelectronics Laser Blue (Blue Ray!)

- SiC much more used and studied in Power Electronics but also in space → wider gap → less sensibility to Cosmic Ray, impact ionization (CAL4 is silicon and is less sensible too→ exploit but is an exception)

Still cost gap vs Silicon of 1 order of magnitude

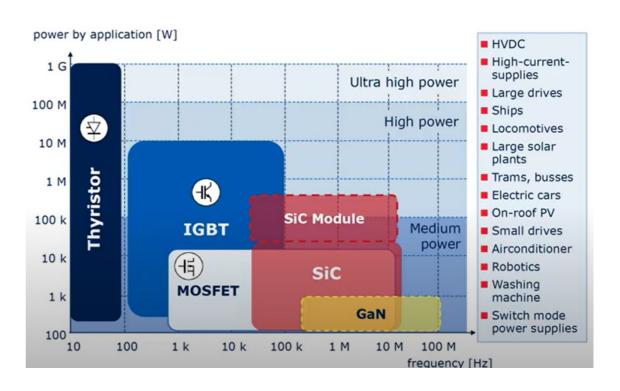

2011 forecast (source IFX) on Power vs Frequency application (will expand more in area typically served by silicon (lower frequency and higher power) the more cost optimization will happen

## **IFX 2011**

# Esempi di convertitori DC-DC "leggeri", "ottimizzati nei costi" e ad "alta efficienza" per automotive

#### Product Portfolio **Power Modules** Shower Power® Technology Direct Pressed Die **DCM**<sup>TM</sup> eMPack® Flexible Design through Customization High Performance Package for e-mobility Si IGBT and full silicon carbide MOSFET technology Silicon carbide MOSFET and full silicon carbide technology 750V/1200V half-bridge design for up to 900 A. 750V / 1200V Sixpack compatible package for up to 900A DBB Sintering Technology for high reliability Double Sided Sintering package for automotive grade reliability Low thermal resistance thanks to ShowerPower®3D Low thermal resistance thanks to DPD Technology Robust molded module packaging, Flexible cooler arrangements low warpage and reliable mechanical integration 2.5nH package stray inductance including terminals Highest power density Multisourcing thanks to chip independency Multisourcing thanks to chip independency

Peak power of Vicor´s automotive product line modules:

BCM6135-A06 800V to 48V and 48V to 800V – unregulated 2.5 kW

DCM3735-AN2 48V to 12V and 12V to 48V – regulated 2.0 kW and

PRM37355-AB4 48V to 48V – regulated 2.5 kW.

- Vantaggi chiave

- Riduzione della massa e del peso e quindi del costo (nelle applicazioni automotive è un aspetto chiave)

- Miglioramento efficienza, riduzione dei consumi

- Fonti:

- Bodo's Power #Novembre 2024

- Semikron Danfoss

## Riferimenti per la fisica quantistica e dei semiconduttori

- [1] Introduzione alla fisica dei Quanti, Giovanni Battimelli, Seminario tenuto al liceo Classico Mamiani di Roma il 20/03/2014. disponibili su YouTube https://youtu.be/ky-55xzuTeQ?si=m26p2y13VZKOuGPQ

- [2] Fisica Matematica Logica, Valerio Pattaro (link consultato il 09/11/2024), https://www.youtube.com/@ValerioPattaro

- [3] C. Mencuccini, V. Silvestrini, Fisica II Elettronagnetismo Ottica, Liguori Editore, Terza edizione Italiana: 1998

- [4] C. Mencuccini, V. Silvestrini, Fisica I Meccanica Termodinamica, Liguori Editore, Seconda edizione Italiana: 1987

- [5] Mazzoldi P., Nigro M., Voci C., Fisica, Eletromagnetismo e Onde, EdiSES, Terza Ddizione Italiana: 2021

- [6] R.P. Feynman, R.B. Leighton, M. Sands, La Fisica di Feynmann, volume 3 Meccanica Quantistica, Zanichelli seconda edizione 2007.

- [7] J. Milman, A. Gravel, Microelettronica, McGraw-Hill, 1994 (edizione italiana)

- [8] R. Muller, T. Kamis, Dispositivi Elettronici nei Circuiti Integrati, Bollati Boringhieri, 1993

- [9] G. Vaccaro, A. Carfagna, L. Piccolella, Lezioni di geometria e algebra lineare -Zanichelli 1999

- [10] Papoulis, A. Probability, Random Variables, and Stochastic Processes Third International Edition - McGraw Hill 19991

- [11] Iannaccone, Giuseppe, Corso di Elettronica di Potenza, Università di Pisa. A.A. 2012-2020, disponibili su YouTube

[22] Fleisch D. Guida allo studio dell'equazione di Schrodinger, Editori Riuniti 2021

- [12] N. Mohan, T.M. Undeland, W. P. Robbins, Power Electronics, Converters, Applications and Design, Third Edition, John wiley & Sons, Inc, 2003

- [13] Neil W. Ashcroft, N. David Mermin Solid State Physics Harcourt inc. 1976. Versione consultata in francese: Physique des solides, EDP Science, 2002.

- [14] Luigi Palumbo, Le Origini della Teoria Quantistica, Appunti del corso di Fisica Moderna 2017-2018, Lezione 4, disponibile on line all'indirizzo https://www.sbai.uniroma1.it/sites/default/files/LEZIONE%20N.4%20-%20CONDUZIONE%20NEI%20SOLIDI.pdf

- [15] Sze S.M., Kwok K.NG. Physics of Semiconductor Devices, 2007, John Wiley & Sons, Inc.

- [16] Sze Simon M. Dispositivi a Semiconduttore Comportamento fisico e Tecnologia, Hoepli 1991.

- [17] Ledermann Leon, Hill Christopher T. Fisica quantistica per poeti, 2013, Bollati Boringhieri (ed. or. 2011 Quantum Physics for Poets)

- [18] Peter W. Atkins, Chimica Fisica, terza edizione condotta sulla quinta edizione inglese, Zanichelli, 1997

- [19] Classic Papers in Physics, Hans Kangro editor, 1972

- [20] Segré Emilio, Personaggi e scoperte della fisica contemporanea, Mondadori 1996

- [21] Segré Emilio, Personaggi e scoperte della fisica classica, Mondadori 1996.

- [23] Pierret F. Robert, *Advanced Semiconductor (vol VI) Fundamentals, 2<sup>nd</sup> edition,* Prentice Hall 2003

https://nanohub.org/courses/sfun (Mark Lundstrom, Perdue University, ultimo accesso al link: 16/03/2025)

### Riferimenti per la parte di elettronica di potenza

- [1] Iannaccone, Giuseppe, Corso di Elettronica di Potenza, Università di Pisa. A.A. 2012-2020, disponibili su YouTube

- [2] A. Volke, M. Hornkamp, *IGBT Modules Technologies, driver and applications*, Infineon Technologies AG, Third edition, 2017

- [3] A. Wintrich, U. Nicolai, W. Tursky, T. Reimann, *Application Manual Power Semiconductors*, SEMIKRON International GmbH, 2nd revised edition 2015

- [4] J. Lutz, H. Schlangenotto, U. Scheuermann, R. De Doncker, Semiconductor Power Devices Physics, Characteristics, Reliability, Springer, 2011

- [5] N. Mohan, T.M. Undeland, W. P. Robbins, *Power Electronics, Converters, Applications and Design*, Third Edition, John wiley & Sons, Inc, 2003

- J. P. Uyemura, Fundamentals of MOS Digital Integrated Circuits, Addison-Wesley Publishing Cpmpany, 1998

- [7] SEMISEL, SEMIKRON Power Electronic Simulation Tool, https://www.semikron-danfoss.com/service-support/semisel-simulation.html,SEMIKRON-DANFOSS

- [8] PSIM 2021A, Simulation environment for power conversion and motor control, https://powersimtech.com/products/psim/capabilities-applications, POWERSIM

- [9] N. H. E. Weste, K. Eshragan, Principle of CMOS VLSI Design, 2nd edition 1993

- [10] C. Mencuccini, V. Silvestrini, Fisica II Elettronagnetismo Ottica, Liguori Editore, 1998

- [11] J. Milman, A. Gravel, *Microelettronica*, McGraw-Hill, 1994 (edizione italiana)

- [12] M. Santoro, M. Hansmann, M. Muscolino, SEMiX5 Technical Explanations, Revision 03, 23-06-2021 https://www.semikron-danfoss.com/dl/service-support/downloads/download/semikron-technical-explanation-semixr5-en-2021-06-23-rev-03.pdf